# Development of ferroelectric tunnel junction devices based on hafnia zirconia films for neuromorphic applications

Inaugural-Dissertation to obtain the academic degree Doctor rerum naturalium (Dr. rer. nat.) submitted to the Department of Biology, Chemistry, Pharmacy of Freie Universität Berlin by

Keerthana Shajil Nair

Berlin July 2024 This page intentionally left blank

All the work mentioned here was performed at Helmholtz-Zentrum Berlin, in the Institute of Functional Oxides for Energy Efficient IT (QM-IFOX), under the supervision of Prof. Dr. Catherine Dubourdieu from January 2020 to March 2024.

1<sup>st</sup> Reviewer: Prof. Dr. Catherine Dubourdieu

$2^{nd}$  Reviewer: Dr. Stefan Slesazeck

Data of Defense: 14.11.2024

This page intentionally left blank

## Acknowledgment

I would like to express my gratitude to Prof. Dr. Catherine Dubourdieu for providing me with the opportunity to conduct my doctoral research under her supervision at QM-IFOX, Helmholtz-Zentrum Berlin. I am also deeply thankful to Dr. Veeresh Deshpande for his daily supervision and invaluable guidance. Thanks to both of you for introducing me to the fascinating field of Memory Devices.

My sincere appreciation goes to Dr. Stefan Slesazeck for being my second reviewer.

I extend my heartfelt thanks to the BeFerroSynaptic project collaborators, including, but not limited to, the teams from the University of Udine and NaMLab.

Throughout this work, I had the pleasure of collaborating with and befriending some truly remarkable individuals from around the world. I would like to thank Rong Wu, Marco Holzer, Ibukun Olaniyan, and Dr. Florian Maudet for their unwavering support and encouragement from the early stages of my doctoral research. Special thanks to Charlotte Van Dijck, Onur Topark, Valentin Havelke, and Dr. Wassim Hamouda for the fun and joyful moments we shared.

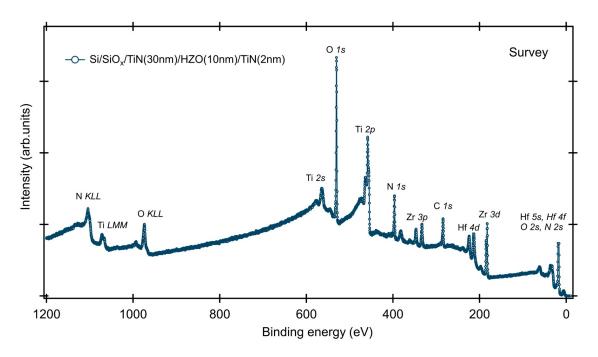

Many individuals have generously contributed their time and efforts to this work, and I extend my heartfelt thanks to each of them. I am grateful to Marco Holzer for developing the ferroelectric HZO layer essential for fabricating my FTJ devices. My thanks also go to Dr. Florian Maudet for developing the ellipsometric model and for his constant support in troubleshooting issues. I appreciate Dr. Wassim Hamouda for providing the XPS analysis whenever needed. Additionally, I am thankful to Marco Holzer, Dr. Sourish Banerjee, Dr. Hamid Raza, Charlotte Van Dijck, and Dr. Wassim Hamouda for performing the ALD depositions and RTP annealings. Your contributions have been invaluable, and I am deeply grateful for your assistance.

I also wish to express my gratitude to Dr. Dong Jik Kim, Dr. Sebastian Schmitt, Dr.

Sandip Lashkare, Dr. Thanh Luan Phan, and Dr. Arnab De for the insightful discussions and valuable knowledge they shared. My thanks extend to Sven Wiesner and Jürgen Albert for their exceptional technical support in the lab.

I am thankful to Dr. Nikoline Hansen and Alisa Ognef for their kindness and administrative support.

I would also like to extend my heartfelt thanks to my friends in Berlin: Gopika Sasikumar, Sreejith Thamban, Siya Anto, Sinju Thomas, Aswin J R, Amal Homer, and Akhil Dev. Their companionship and support helped me maintain a balanced life outside of work, ensuring my well-being and making my time in Berlin truly enjoyable. Special thanks to Rong for always being there for me and providing the wisest advice during crucial moments.

Above all, I express my deepest gratitude and appreciation to my family, who have been my pillars of support throughout this journey. I owe everything to them. My heartfelt thanks go to my father (Achan - Shajil Kumar U), my mother (Amma - Sheeja T P), my sister (Ambi - Gopika S Nair), and my partner (Ashi - Ashish Mishra).

Lastly, I extend my heartfelt thanks to everyone who has offered me kindness, support, and patience throughout my life.

## **Declaration of authorship**

I hereby declare that I alone am responsible for the content of my doctoral dissertation and that I have only used the sources or references cited in the dissertation.

Date: 15.07.2024

Keerthana Shajil Nair

This page intentionally left blank

## Contents

| Ał | ostrac | et       |                                                               | xii  |

|----|--------|----------|---------------------------------------------------------------|------|

| Ζı | ısamr  | nenfass  | sung                                                          | xiii |

| In | trodu  | ction    |                                                               | 1    |

| 1  | Scie   | ntific b | ackground                                                     | 8    |

|    | 1.1    | Ferroe   | electricity                                                   | 8    |

|    |        | 1.1.1    | Fundamental properties                                        | 9    |

|    |        | 1.1.2    | Different types of ferroelectric materials                    | 12   |

|    |        | 1.1.3    | Hafnium-oxide based ferroelectric thin films                  | 15   |

|    |        | 1.1.4    | Models of polarization switching mechanisms                   | 20   |

|    |        | 1.1.5    | Ferroelectricity for memory applications                      | 23   |

|    | 1.2    | Ferroe   | electric tunnel junction (FTJ)                                | 27   |

|    |        | 1.2.1    | Physics of FTJ devices                                        | 29   |

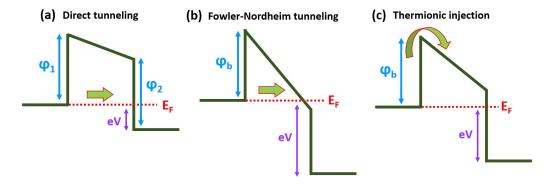

|    |        | 1.2.2    | Mechanisms of charge transport in FTJs                        | 32   |

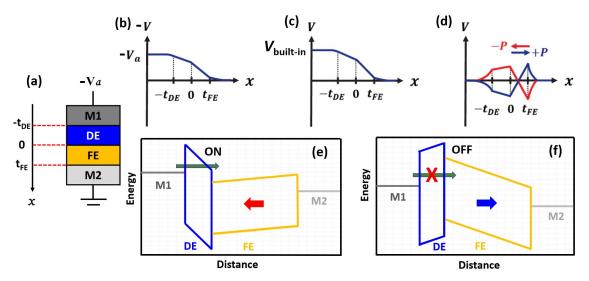

|    |        | 1.2.3    | M-FE-DE-M device architecture for FTJs                        | 34   |

|    | 1.3    | FTJs f   | for neuromorphic computing                                    | 36   |

| 2  | Fab    | rication | and characterization methods                                  | 40   |

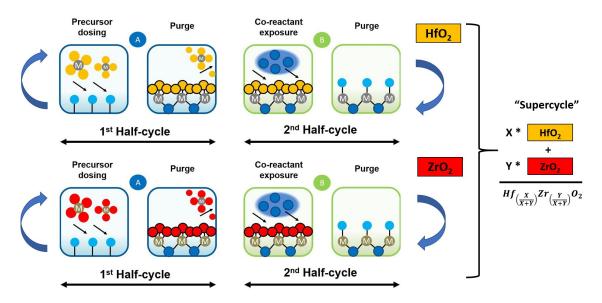

|    | 2.1    | Materi   | ial deposition techniques                                     | 40   |

|    |        | 2.1.1    | Atomic layer deposition (ALD)                                 | 41   |

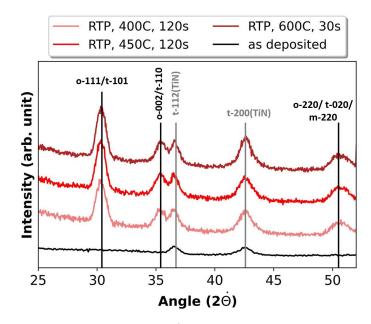

|    |        | 2.1.2    | Optimization of ALD deposited ferroelectric Hafnium-Zirconium |      |

|    |        |          | Oxide                                                         | 42   |

|    |        | 2.1.3    | Sputter deposition                                            | 45   |

|   |     | 2.1.4   | Thermal evaporation                                               | 46  |

|---|-----|---------|-------------------------------------------------------------------|-----|

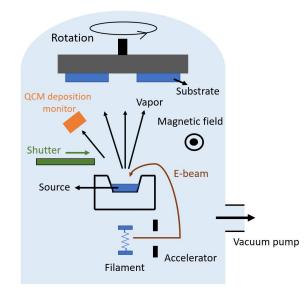

|   |     | 2.1.5   | Electron beam (E-beam) evaporation                                | 47  |

|   | 2.2 | Lithog  | graphy                                                            | 48  |

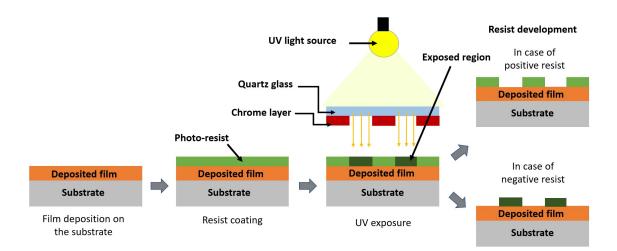

|   |     | 2.2.1   | Photolithography                                                  | 50  |

|   |     | 2.2.2   | Laser lithography                                                 | 50  |

|   | 2.3 | Thickr  | ness, structural, and chemical analysis                           | 51  |

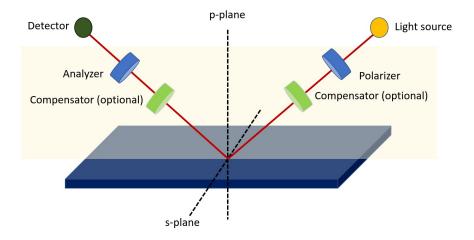

|   |     | 2.3.1   | Ellipsometry                                                      | 52  |

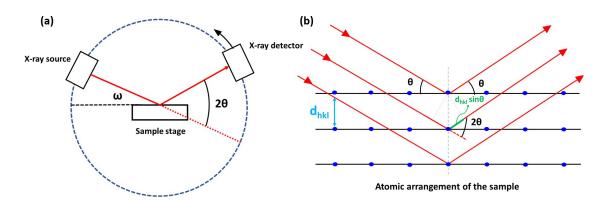

|   |     | 2.3.2   | Grazing incidence X-ray diffraction (GIXRD)                       | 54  |

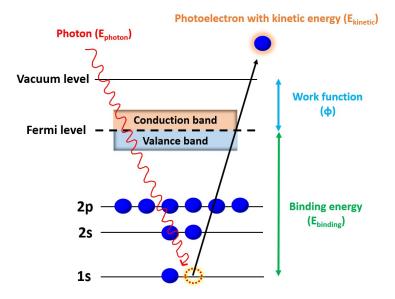

|   |     | 2.3.3   | X-ray photoelectron spectroscopy (XPS)                            | 56  |

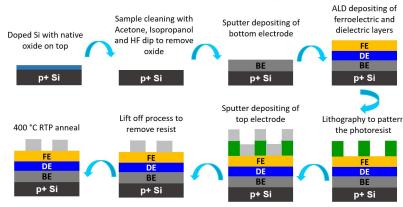

|   | 2.4 | Device  | e fabrication process flow                                        | 59  |

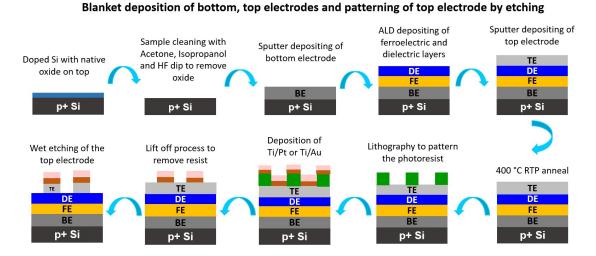

|   |     | 2.4.1   | Blanket bottom electrode and lift-off top electrode               | 59  |

|   |     | 2.4.2   | Blanket bottom electrode and top electrode patterned by etching . | 61  |

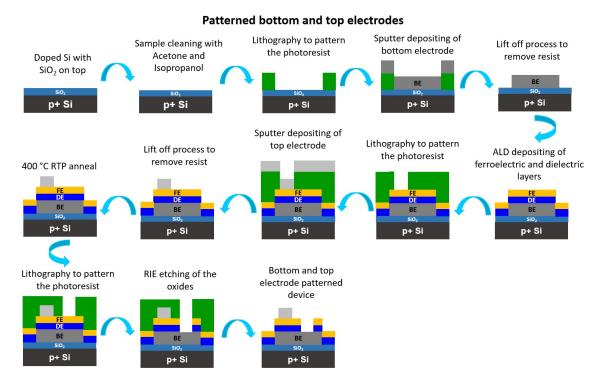

|   |     | 2.4.3   | Patterned bottom and top electrodes                               | 62  |

|   | 2.5 | Electri | ical Characterization                                             | 63  |

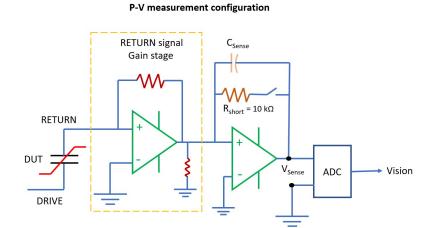

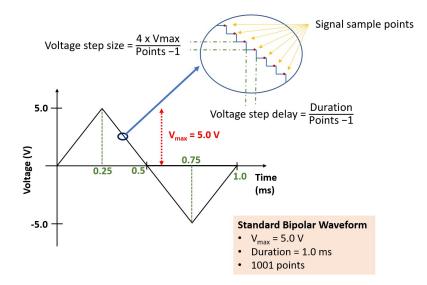

|   |     | 2.5.1   | Polarization-Voltage (P-V) measurement                            | 63  |

|   |     | 2.5.2   | Current-voltage (I-V) measurement                                 | 66  |

|   |     | 2.5.3   | PUND P-V measurement                                              | 67  |

|   |     | 2.5.4   | Small signal capacitance-voltage (C-V) measurement                | 71  |

|   |     | 2.5.5   | Reset-read-set-read measurements                                  | 72  |

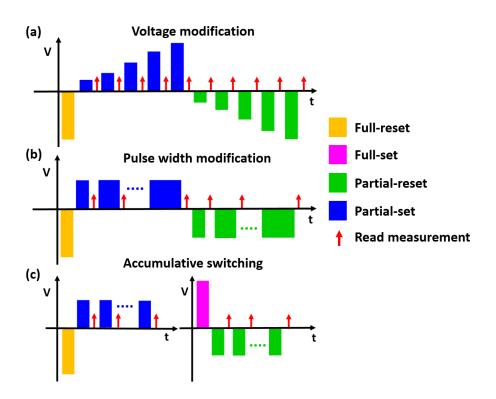

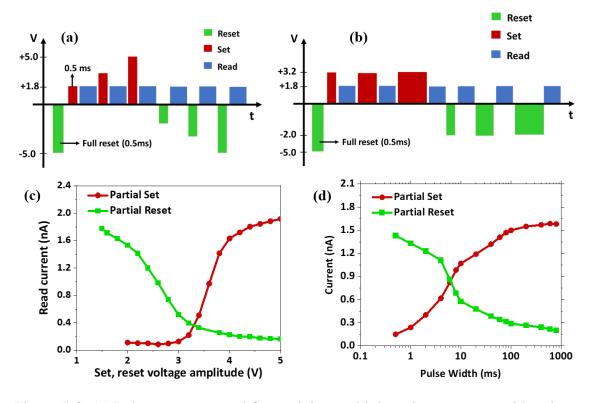

|   |     | 2.5.6   | Partial switching measurements for multiple resitance states      | 73  |

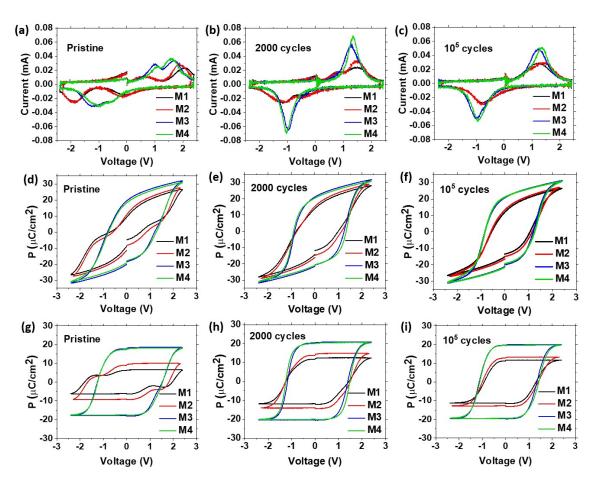

|   | 2.6 | Electri | cal characterization of M-FE-M stacks                             | 75  |

| • | וית |         | TT /· /·                                                          | 00  |

| 3 |     |         | J Investigation                                                   | 80  |

|   | 3.1 |         | uction                                                            | 80  |

|   | 3.2 |         | of dielectric positioning                                         | 82  |

|   | 3.3 | Effect  | of metal electrode positioning                                    | 88  |

|   | 3.4 | Optim   | um FTJ Stack                                                      | 93  |

|   | 3.5 | Effect  | of dielectric thickness                                           | 96  |

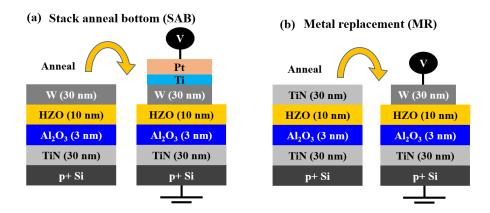

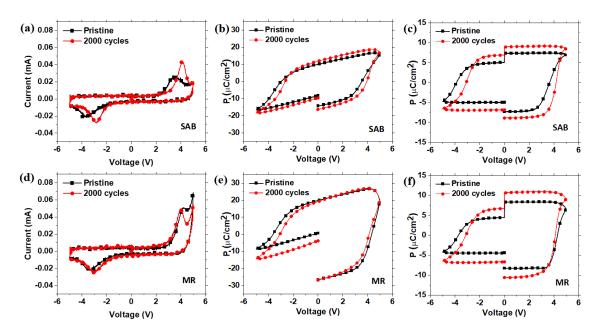

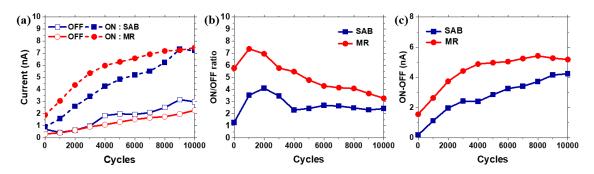

|   | 3.6 | Impact  | t of sample processing                                            | 98  |

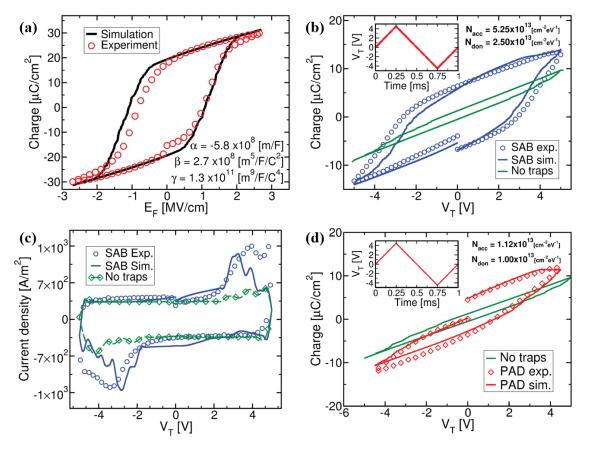

|   | 3.7 | Quanti  | ification of charge traps in the FTJ stack                        | 111 |

|   | 3.8 | Confir  | mation of charge traps through C-V and polarization measurements  | 114 |

|   | 3.9 | Summ    | ary                                                               | 117 |

| 4  | Imp     | act of electrical parameters on the device performance                         |

|----|---------|--------------------------------------------------------------------------------|

|    | 4.1     | Introduction                                                                   |

|    | 4.2     | Cycling waveform dependent wake-up and ON/OFF ratio                            |

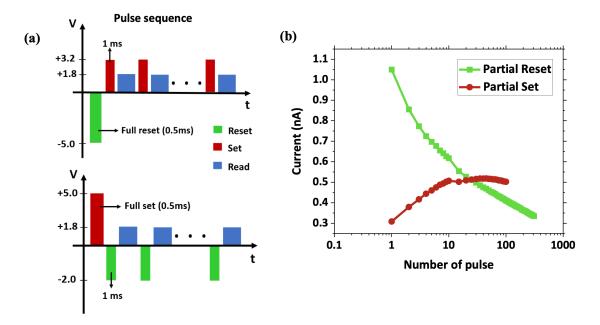

|    | 4.3     | Reset, Set pulse modification for multiple resistance states stabilization 138 |

|    | 4.4     | Summary                                                                        |

| 5  | CM      | OS integration of FTJ device                                                   |

|    | 5.1     | Introduction                                                                   |

|    | 5.2     | Fabrication of FTJ devices on CMOS chip                                        |

|    | 5.3     | Stand-alone FTJ characterization                                               |

|    | 5.4     | Transistor measurements                                                        |

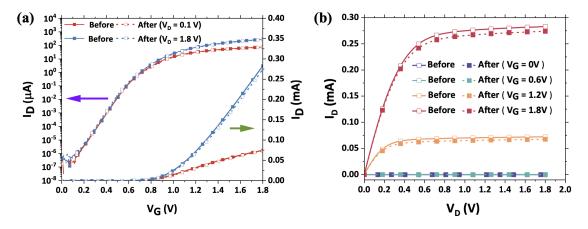

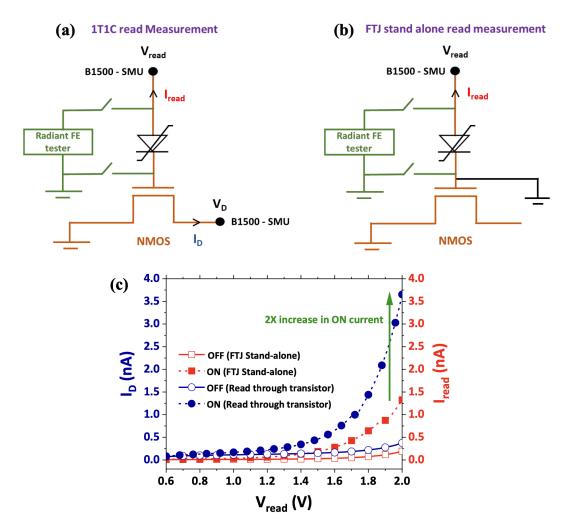

|    | 5.5     | 1T1C measurement to amplify FTJ output                                         |

|    | 5.6     | Summary                                                                        |

| Co | onclus  | sion                                                                           |

| Bi | bliog   | raphy                                                                          |

| Li | st of l | Publications                                                                   |

| Li | st of A | Abbreviations                                                                  |

## Abstract

This thesis focuses on the development of FTJ devices using a  $Hf_{0.5}Zr_{0.5}O_2$  (HZO) ferroelectric layer, demonstrating their compatibility with CMOS integration and their applicability in neuromorphic hardware. A bilayer structure comprising metal- ferroelectric-dielectric-metal layers with a ~ 10 nm HZO ferroelectric layer and a thin tunneling  $Al_2O_3$  layer has been investigated.

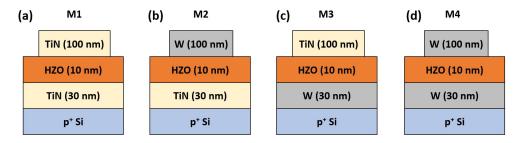

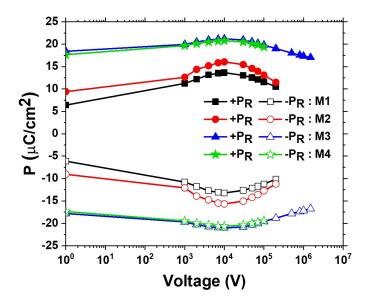

We examine the impact of dielectric positioning, metal electrode placement (with W and TiN), and dielectric thickness on device performance. Additionally, we explore the role of charge traps in the dielectric or at the dielectric-ferroelectric interface, and the influence of the fabrication process on charge trap density and polarization switching behavior. W bottom electrode is found to give optimized device performance, and positioning  $Al_2O_3$  next to the bottom electrode further enhances the device performance in terms of ON current and ON/OFF ratio. Furthermore, longer pulses are necessary to stabilize higher remnant polarization due to charge trap dynamics.

We also analyze various electrical parameters affecting FTJ device performance, demonstrating that the cycling waveform significantly influences the wake-up process and the resulting remnant polarization in TiN-Al<sub>2</sub>O<sub>3</sub>-HZO-W FTJ devices. Square waveforms outperform triangular waveforms, yielding higher remnant polarization ( $P_R$ ) post-wake-up. By employing an asymmetric waveform for field cycling and adjusting the pulse width, the  $P_R$  and the ON/OFF ratio after wake-up are significantly improved.

Finally, we explore the integration of bilayer FTJ devices into CMOS back-end-ofline (BEOL) processes, demonstrating a 1T1C circuit by connecting an FTJ in the BEOL with an nMOS transistor in the front-end-of-line. Measurements on standalone FTJ devices in the BEOL reveal an ON/OFF ratio of 18 and an ON current density of 24.5  $\mu$ A/cm<sup>2</sup>. Crucially, BEOL fabrication has negligible impact on transistor characteristics, and the 1T1C circuit exhibits a 2.6-fold amplification of the FTJ ON current. The FTJ devices integrated on the CMOS-BEOL demonstrate multiple resistance states with the application of partial switching Reset and Set pulses. These FTJ devices have the potential to be utilized in neuromorphic hardware systems.

## Zusammenfassung

Diese Arbeit konzentriert sich auf die Entwicklung von FTJ-Bauelementen unter Verwendung einer ferroelektrischen Hf<sub>0,5</sub>Zr<sub>0,5</sub>O<sub>2</sub> (HZO)- Schicht und demonstriert sowohl die CMOS- Integrierbarkeit der Bauteile als auch deren Anwendbarkeit für neuromorphe Hardware. Hinsichtlich dieser Aufgabe wurden Doppelschichtstrukturen bestehend aus Metall-Ferroelektrikum-Dielektrikum-Metall-Schichten, mit einer ~ 10 nm großen ferroelektrischen HZO-Schicht und einer dünnen Al<sub>2</sub>O<sub>3</sub> Tunnelschicht, untersucht.

Wir erforschten unter anderem die Auswirkungen der Positionierung des Dielektrikums, der Platzierung der Metallelektroden (jeweils aus W und TiN) und auch der Dicke des Dielektrikums hinsichtlich auf der Bauelement- Leistung. Außerdem studierten wir die Rolle von sogenannten Ladungsfallen im Dielektrikum und/oder an der dielektrischferroelektrischen Grenzfläche, sowie den Einfluss des Herstellungsprozesses auf die Ladungsfallendichte und das Polarisationsschaltverhalten. Zuerst konnte gezeigt werden, dass die W-Bodenelektrode eine optimierte Bauelementleistung bietet. Ebenso verbesserte die direkte Positionierung von Al<sub>2</sub>O<sub>3</sub> neben der Bodenelektrode die Bauelementleistung hinsichtlich des "ON current" und des "ON/OFF"- Verhältnisses. Wir beobachteten zudem, dass längere Pulse erforderlich sind, um eine höhere Restpolarisation aufgrund von Ladungsfallendynamiken zu stabilisieren.

Im nächsten Schritt analysierten wir verschiedene elektrische Parameter, die die Leistung von FTJ- Bauelementen beeinflussen, und zeigten, dass die zyklische Wellenform den sogenannten Aufwachprozess und die daraus resultierende Restpolarisation in TiN-Al<sub>2</sub>O<sub>3</sub>-HZO-W FTJ-Bauelementen erheblich beeinflusst. Rechteckige Wellenformen übertreffen dreieckige Wellenformen und führen zu einer höheren Restpolarisation nach dem Aufwachen. Durch die Verwendung einer asymmetrischen Wellenform für den Feldzyklus und die Anpassung der Pulsbreite wurde die Restpolarisation und das ON/OFF-Verhältnis nach dem Aufwachprozess deutlich verbessert.

Schließlich demonstrierten wir die Integration von zweischichtigen FTJ-Bauelementen im CMOS-Back-End-of-Line (BEOL)-Prozess mit Hilfe einer 1T1C-Schaltung, indem wir einen FTJ im BEOL mit einem nMOS-Transistor im Front-End-of-Line verbanden. Messungen an eigenständigen FTJ-Bauelementen im BEOL ergaben ein ON/OFF- Verhältnis von 18 und eine ON-Stromdichte von 24,5  $\mu$ A/cm<sup>2</sup>. Entscheidend ist, dass die BEOL-Fertigung vernachlässigbare Auswirkungen auf die Transistoreigenschaften hat und die 1T1C-Schaltung eine 2,6-fache Verstärkung des FTJ- On-Currents aufweist. Die auf dem CMOS-BEOL integrierten FTJ-Bauelemente zeigen zudem mehrere Widerstandszustände bei der Anwendung von partiellen Reset- und Set-Pulsen. Diese FTJ-Bauelemente haben daher das Potenzial, in neuromorphen Hardwaresystemen eingesetzt zu werden.

## Introduction

Memory devices are one of the key components of computing systems. It is a necessary part of almost every digital computing system, enabling the execution of software applications and the preservation of user data.

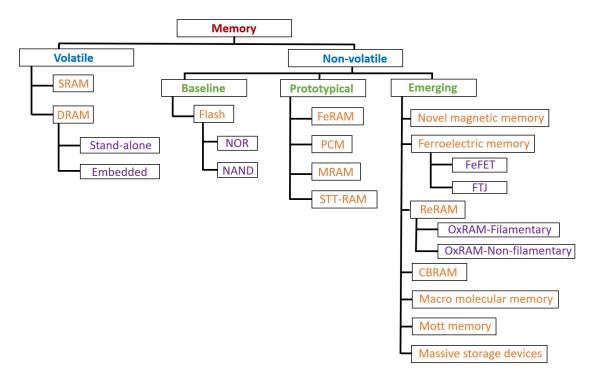

The demand for advanced memory solutions has grown significantly due to the rapid integration of technology into daily life, mainly through the internet of things (IoT). Hence, there is a need for innovations that offer high storage density, fast operations, low power consumption, and cost-effectiveness. While existing memory technologies like static random access memory (SRAM), dynamic random access memory (DRAM) and flash memory have driven the evolution of digital devices, they face significant limitations that challenge their suitability for future demands. SRAM and DRAM are utilized for fast access but are volatile. Hence they are limited to data storage during computations. A single SRAM cell consists of several transistors (typically six), which results in a larger SRAM size compared to DRAM. This larger size results in lower storage density and can limit the scalability [1]. DRAM, being volatile, requires constant power to maintain data, leading to high energy consumption [2, 3]. For long-term data storage, the main memory technology in use is Flash memory owing to its non-volatility. However, flash suffers from slow write and limited endurance [4, 5]. Furthermore, flash device process technology is not compatible with advanced Complementary Metal-Oxide-Semiconductor (CMOS) technology on which digital processors are fabricated. Therefore, new non-volatile memory technologies are being developed, as shown in Figure 1 to enable on-chip memory for emerging data intensive applications.

In recent years, the use of artificial intelligence in various aspects of human lives has increased significantly. Applications such as facial recognition, image recognition, pattern classification, autonomous vehicles, and robotics are just a few examples [6–8]. While these tasks are currently executed on digital CMOS computational platforms, the data-heavy applications anticipated in the future necessitate hardware that can make autonomous decisions [9]. This highlights the need to move beyond the traditional von-Neumann computational architecture, which involve extensive data transfers between the central processing units (CPUs) and main memory. This constant data exchange elevates

power consumption and prolonged data processing duration which is collectively referred as the Von-Neumann bottleneck [10].

Figure 1: Schematic overview of the memory technology landscape. A classification of memory types showing the hierarchy of volatile and non-volatile memory technologies. Volatile memories include SRAM and DRAM, which are further divided into stand-alone and embedded types. Non-volatile memories are categorized into baseline (Flash, NOR, NAND), prototypical (FeRAM, PCM, MRAM, STT-RAM), and emerging technologies. Emerging non-volatile memories include novel magnetic memory, ferroelectric memory (with FeFET and FTJ), ReRAM (with OxRAM filamentary and non-filamentary), CBRAM, macro molecular memory, Mott memory, and massive storage devices. Figure reproduced from [11].

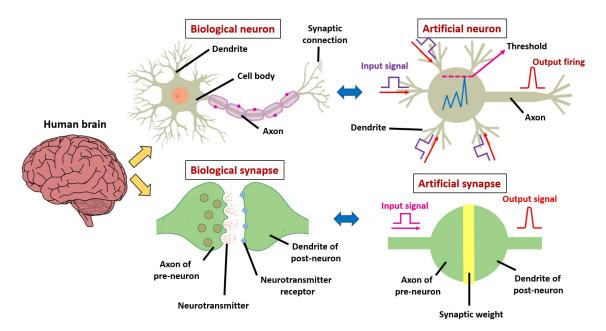

Neuromorphic computing represents a paradigm shift in the computational technology, inspired by the architecture of the human brain [12, 13]. This approach to computing involves the design of electronic systems that mimic the brain's structure and processing methods, aiming to achieve the efficiency and adaptability of the biological neural networks [10]. Neuromorphic systems utilize specialized hardware, such as artificial neurons and synapses, which allow them to process information in a highly parallel and energyefficient manner. The neural networks can be classified into two groups namely, artificial neural networks (ANN) and spiking neural networks (SNN). The ANN processes information using layers of neurons that activate continuously and are typically trained with methods like backpropagation [14, 15]. Backpropagation is an algorithm used to train ANNs by iteratively adjusting weights to minimize the error between the predicted and actual outputs. In contrast, SNN mimics biological brain activity more closely, using discrete spikes (electrical pulses) to communicate between neurons and incorporating the timing of these spikes into their computation. SNNs often utilize unique learning rules such as spike-timing-dependent plasticity (STDP) and are known for their energy efficiency [16]. Emerging memory devices that mimic the functionality of biological synapses and neurons can be used as neuromorphic hardware components [9]. The requirements for such memories are as follows,

- Ability to program the conductance in analog fashion

- Low-voltage operation

- · Fast switching

- Possibility to scale the devices for dense integration.

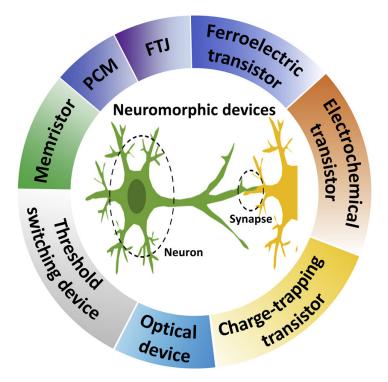

Figure 2 illustrates the emerging memory devices that have shown potential to be used as components in neuromorphic hardware systems. Filamentary memristors, phase change memories (PCM), and ferroelectric tunnel junctions (FTJ) are 2-terminal devices. However, ferroelectric transistors, electrochemical transistors, and charge-trapping transistors are 3-terminal devices. Even though these devices have successfully demonstrated functions of neurons or synapses as proof of concept [10, 17–21], the large scale implementation needed for real world applications requires them to be compatible with CMOS technology [9]. For ferroelectric RAM, the technology used hitherto was based on ferroelectric perovskite materials. However, these could not be scaled to low dimensions limiting their integration in advanced CMOS technology. The discovery of ferroelectricity in Hafnium oxide (HfO<sub>2</sub>) [22] brought a solution to the scalability issue faced by conventional perovskite based ferroelectric materials and HfO<sub>2</sub> is widely used as a high-k dielectric material in CMOS processes, particularly for gate oxides in transistors [23]. The ease of integration with existing CMOS technology has increased interest in hafnium-based ferroelectric memory devices.

Ferroelectric materials exhibit spontaneous electric polarization that can be reversed by an external electric field, providing a mechanism for non-volatile memory that does

Figure 2: Emerging memory devices for neuromorphic applications. Figure reproduced from [10].

not require power to maintain data state. As polarization switching is an electric-field driven phenomena (with only displacement current flowing), low power consumption can be achieved during memory write/erase operations. This characteristic makes ferroelectric memories particularly attractive for energy-sensitive applications such as wearable technology and IoT devices. FTJs leverage these properties to create memory devices that offer not only reduced power consumption but also the potential for high-density integration due to its reduced footprint from 2-terminal architecture. Additionally, FTJs support multi-level data storage which is essential for neuromorphic applications. By using HfO<sub>2</sub> based ferroelectric layer, they become CMOS compatible and with a possible reduction in the processing temperature to  $\leq$ 450 °C, they can even be integrated to the back-end-of-line (BEOL) of CMOS technology [23].

This doctoral thesis addresses the need for advanced on-chip non-volatile memory technologies by exploring FTJ devices based on a  $Hf_{0.5}Zr_{0.5}O_2$  (HZO) ferroelectric layer. The research focuses on metal-ferroelectric-dielectric-metal (M-FE-DE-M) FTJ devices,

which utilize a thicker ferroelectric layer (approximately 10 nm) while maintaining a high ON current and ON/OFF ratio. Tungsten (W) and Titanium Nitride (TiN) metals are selected as the electrodes for the M-FE-DE-M FTJ devices due to their compatibility with CMOS technology. The chosen HZO crystallization temperature of 400°C ensures that these devices are CMOS-BEOL compatible. Recognizing the significant impact of interface quality on the performance of tunnel junction devices, this work commences with the optimization of the M-FE-DE-M FTJ device architecture. This involves a detailed investigation into the effects of dielectric and metal electrode positioning to enhance device performance. Subsequently, this study examines the influence of dielectric thickness on the properties of the FTJ devices. Additionally, this research explores various fabrication process flows to determine their impact on device performance, aiming to optimize the fabrication process for these FTJ devices.

This work aims to investigate the wake-up effect observed in the HZO ferroelectric layer, where polarization increases with electric field cycling, as seen in FTJ devices based on HZO layers. The objective is to study the role of field cycling operations on FTJ device properties by utilizing different waveforms for field cycling. Optimizing the cycling waveform is expected to achieve the highest remnant polarization ( $P_R$ ) and ON/OFF ratio from a given FTJ stack. Additionally, the research seeks to modify electrical parameters of Reset and Set pulses to enable partial polarization switching in the ferroelectric layer, thereby demonstrating multiple resistance states in the FTJ devices. These multiple resistance states are crucial for neuromorphic applications, and achieving this in the devices is a primary objective of this study.

This research seeks to demonstrate the CMOS-BEOL integration of optimized FTJ devices and characterize their properties using optimized electrical parameters. Additionally, it seeks to study the impact of FTJ integration on CMOS front-end transistors by analyzing their properties before and after the integration process. Furthermore, the research aims to utilize front-end nMOS transistors to amplify the read currents from the FTJ devices through a 1T1C circuit configuration.

This work has been carried out and partly funded in the framework of the Horizon 2020 European project "BEOL Technology Platform based on Ferroelectric Synaptic Devices for Advanced Neuromorphic Processors" (BeFerroSynaptic - (no. 871737)). This

EU project (January 2020 - December 2023) was coordinated by Dr. Stefan Slesazeck from NamLab GmbH in Dresden. The objective of this project was to develop advanced neuromorphic processors by integrating ferroelectric synaptic devices such as FTJs and FeFETs into CMOS technology, enhancing device performance, and demonstrating practical applications in AI and edge computing, thereby significantly reducing power consumption and improving efficiency.

### **Organization of this thesis**

This thesis is structured into five chapters, each addressing different aspects of FTJ memory devices for neuromorphic applications.

In Chapter 1, we present the scientific background and a comprehensive literature review. It covers the fundamental properties and various types of ferroelectric materials, with a focus on hafnium-oxide-based ferroelectric thin films. The chapter explores the application of ferroelectricity in memory devices, polarization switching mechanisms, and the physics of FTJ devices. It also delves into charge transport mechanisms in FTJs, the M-FE-DE-M device architecture for FTJs, and the application of FTJs in neuromorphic computing.

In Chapter 2, we detail the methods used for fabricating and characterizing the FTJ devices. This includes material deposition techniques, lithography methods, thickness and chemical analysis methods, the device fabrication process flow, and various electrical characterization techniques. Additionally, the characterization of M-FE-M capacitor structures is also presented.

In Chapter 3, we investigate the bilayer structure (M-FE-DE-M) of FTJ devices, focusing on the effects of dielectric positioning, metal electrode positioning, dielectric thickness, sample fabrication process flows, and the significance of charge traps within the FTJ stack.

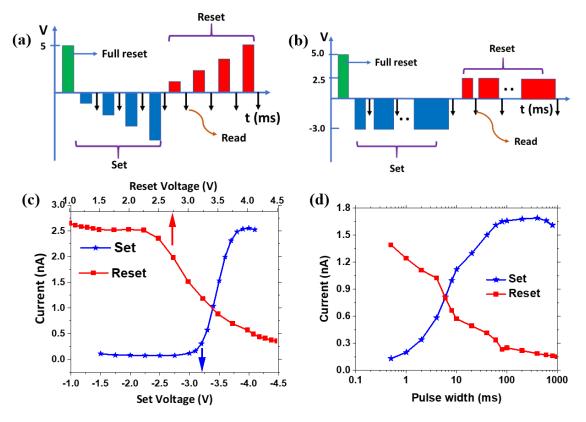

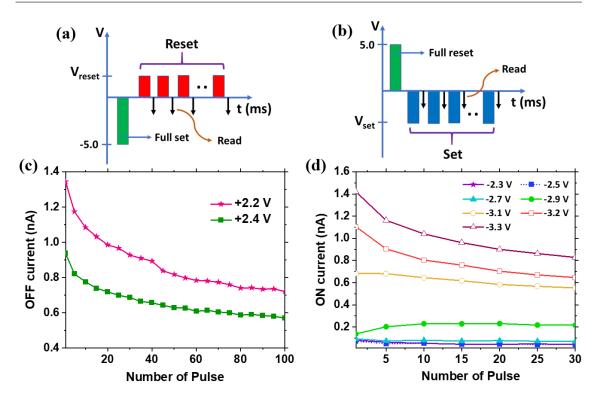

In Chapter 4, we analyze the impact of various electrical parameters on FTJ device performance. This includes examining the effects of cycling waveforms on the wake-up behaviour and ON/OFF ratio of the FTJ devices, as well as utilizing modified Reset and Set pulses to achieve multiple resistance states in the FTJ devices.

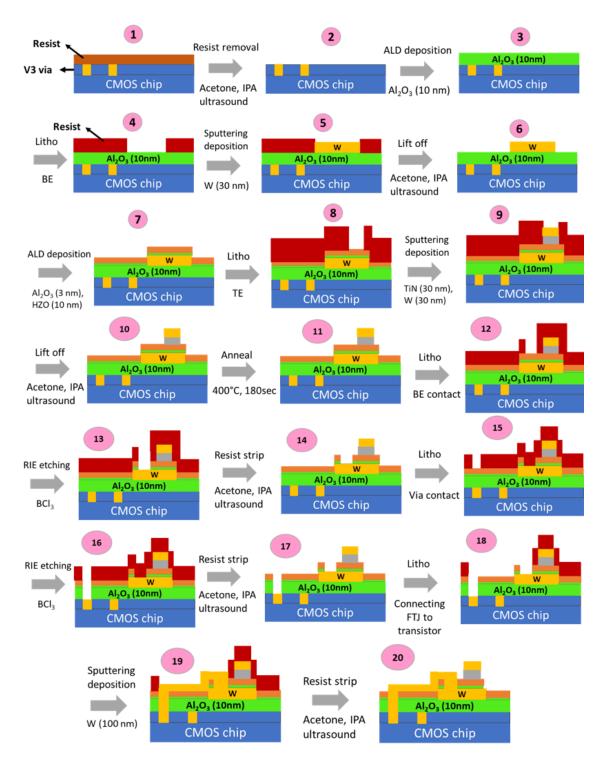

In Chapter 5, we explore the integration of optimized FTJ devices with CMOS-BEOL,

detailing the fabrication process flow for CMOS integration of FTJs. Stand-alone FTJ and front-end transistor measurements are performed to characterize the components individually. Subsequently, the FTJ devices are connected to the front-end transistors to create a 1T1C circuit configuration, which is used to amplify the read currents from the FTJ. The results of these experiments are presented in this chapter.

Finally, we summarize the key findings of our research, highlighting the contributions and implications of the study and suggest potential future research directions to further advance the field of FTJ memory devices for neuromorphic applications.

## Chapter 1

## Scientific background

### **1.1 Ferroelectricity**

The term "ferroelectricity" is similar to "ferromagnetism" in magnets, where materials exhibit a permanent magnetic moment. However, in ferroelectric materials, this concept applies to electric polarization instead of magnetism. Ferroelectricity is a property shown by certain materials that exhibit a spontaneous electric polarization. These materials can maintain an electric dipole moment even in the absence of an external electric field. This exhibited polarization is not fixed and can be reversed by the application of an external electric field. The ability to switch the direction of polarization supports many of the practical applications of ferroelectric materials. Key characteristics of ferroelectric materials include:

- **Spontaneous Polarization:** The natural ability of the material to form a dipole moment.

- Switchable Polarization: The direction of the polarization can be switched or reversed by applying an external electric field.

- **Hysteresis Loop:** When the polarization as a function of the electric field is plotted, ferroelectric materials show a hysteresis loop, similar to ferromagnetic materials. This property is useful for memory storage devices, as the state of the polarization (up or down) can represent binary information.

### **1.1.1 Fundamental properties**

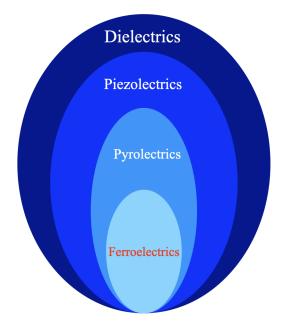

Dielectrics are insulating materials that do not conduct electricity but can support electric fields, which allows them to store electrical energy. Within this category fall the piezoelectrics, materials that generate an electric charge in response to mechanical stress. Piezoelectrics further include a subset known as pyroelectrics, which generate an electric charge when the temperature is varied. Ferroelectric materials are a specialized group within pyroelectrics, characterized by their ability to retain their electric polarization after an external electric field is removed. Each category represents a progressively specific type of behaviour related to the material's interaction with electrical and mechanical forces [24]. This classification is schematically shown in Figure 1.1.

Figure 1.1: Pictorial representation of various subgroups of dielectric materials.

In a ferroelectric material, the electric displacement (D) is defined as

$$\mathbf{D} = \epsilon_0 \mathbf{E} + \mathbf{P} \tag{1.1}$$

where  $\epsilon_0$ , E and P are the vacuum permittivity, electric field, and polarization, respectively. This polarization can be expressed in terms of the spontaneous polarization (P<sub>S</sub>) and the linear dielectric response as follows

$$P = \epsilon_0 \chi E + P_S, \tag{1.2}$$

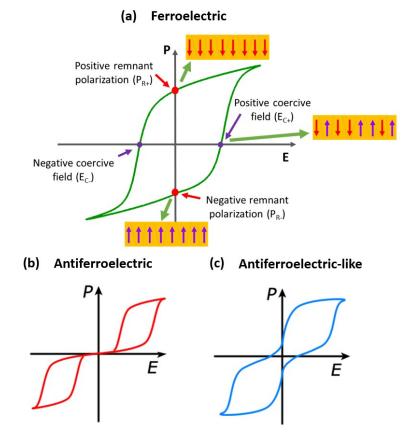

where  $\chi$  is the electrical susceptibility of the medium. A linear dielectric shows a linear polarization response to the applied electric filed. However, ferroelectric material shows a hysteresis loop as shown in Figure 1.2(a) in response to the applied electric filed. The Y-axis intercepts in the positive and negative sides are the positive and negative remnant polarization (P<sub>R</sub>) values. It is the residual polarization that remains in a ferroelectric material after the external electric field is removed. The X-axis intercepts in the positive and negative sides are the coercive field (E<sub>C</sub>) values. It represents the external electric field that must be applied to a material to reduce its polarization to zero from the remnant value. The Curie temperature (T<sub>C</sub>) of a ferroelectric material is the temperature above which the material loses its ferroelectric properties and becomes paraelectric. At temperatures below the T<sub>C</sub>, the material exhibits spontaneous electric polarization.

Figure 1.2: Schematic showing three types of electrical polarization responses to applied electric fields: (a) A single loop typical of ferroelectrics; (b) A double hysteresis loop with zero remnant polarization, typical of antiferroelectric (AFE) state; (c) A pinched hysteresis loop with small but noticeable remnant polarization. We call this an antiferroelectric-like state. The figures (b) and (c) are adapted from [25]. The domain orientations for different polarization states are shown in the inset of (a).

The ferroelectric material has a non-centrosymmetric crystal structure, resulting in a non-centrosymmetric distribution of charges in the unit cell. This results in the formation of the dipole with a dipole moment p. The macroscopic polarization P is the sum of individual dipole moments normalized by the volume of the unit cell. Although charges are balanced within the bulk of the material, there are unbalanced charges at the surface of the solid. Therefore, polarization can also be described in terms of surface charge, and it shares the same units as charge density. The regions within a material where the electric dipoles are aligned in a uniform direction are known as the domains (shown in Figure 1.2(a)). These domains form as a result of the minimization of the material's free energy. In a single-domain ferroelectric, the coercive field is represented by a single value. However, in a ferroelectric material with multiple domains, each domain may possess a distinct coercive field. This variability leads to a distribution of coercive fields, which causes a tilt in the ferroelectric hysteresis loop.

When there are several domains in the material and the adjacent dipoles are oriented in anti-parallel configurations, this might lead to a net zero polarization in the absence of an external electric field. Such a state is known as an antiferroelectric state. This state gives a double hysteresis loop as polarization response to the external electric field, see Figure 1.2(b). When there is a coexistence of both ferroelectric and antiferroelectric regions, the material shows a pinched hysteresis loop as shown in Figure 1.2(c). This type of hysteresis loop is referred to as an antiferroelectric-like hysteresis loop [25].

Ferroelectricity and antiferroelectricity are phenomena associated with the spontaneous alignment of electric dipoles within a material, which can be described using the Landau-Ginzburg formalism. This formalism is a thermodynamic approach that leverages the concept of order parameters to describe phase transitions, including those in ferroelectrics and antiferroelectrics [26, 27]. Ferroelectricity is characterized by a uniform alignment of electric dipoles in the same direction, which can be modelled using a single order parameter representing the polarization magnitude and direction. The Landau-Ginzburg theory for ferroelectricity involves a free energy expansion in terms of the polarization order parameter, where the stability and change of phases can be influenced by temperature, electric field, and mechanical stress. Antiferroelectricity, on the other hand, involves a more complex arrangement where adjacent dipoles are oriented in opposite directions, leading to a cancellation of the overall polarization. This requires a multicomponent order parameter that can describe the relative orientations of the dipoles.

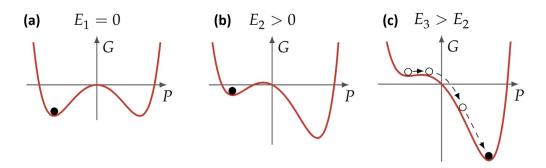

Figure 1.3: (a) Gibbs free energy potential (G) in the absence of external field (E). (b) Asymmetric potential landscape under the influence of non-zero electric field. (c) Destabilization of one polarization state by the application of a higher electric field, leading to switching of polarization. [Reproduced from [28]]

In a simple *uniaxial* ferroelectric<sup>1</sup>, the polarization can exist in two stable states, which correspond to the two polarization directions (+P and -P). In the absence of an external field, there is no energy difference between these two states. The Gibbs free energy (G) of the ferroelectric material can be described as,

$$G = -EP + \frac{\alpha}{2}P^2 + \frac{\beta}{4}P^4 + \frac{\gamma}{6}P^6 + \dots, \qquad (1.3)$$

where  $\alpha$ ,  $\beta$  and  $\gamma$  are the Landau coefficients which control the order of the phase transition. Generally, it is not necessary to consider orders of P higher than six. The term -EP accounts for the contribution from the external electric field. Application of a positive (negative) electric field reduces the Gibbs free energy of the positive (negative) polarization. A stable state is achieved by minimizing G. This mechanism explains how polarization is switched by applying an external electric field, as illustrated in Figure 1.3.

#### **1.1.2** Different types of ferroelectric materials

Historically, the concept of ferroelectricity dates back to 1912 when Erwin Schrödinger first proposed the term [29, 30]. However, the first actual discovery of ferroelectricity occurred in 1921 with Rochelle salt (NaKC<sub>4</sub>H<sub>4</sub>O<sub>6</sub>·4H<sub>2</sub>O) [31]. The instability against

<sup>&</sup>lt;sup>1</sup>Uniaxial ferroelectric materials exhibit spontaneous electric polarization along a single crystallographic axis, with their ferroelectric properties and polarization switching confined to that direction.

dehydration and the complex structure of the Rochelle salt restricted the early work on ferroelectrics [32]. In 1935, the discovery of ferroelectricity in potassium dihydrogen phosphate (KH<sub>2</sub>PO<sub>4</sub>), abbreviated as KDP, marked a significant advancement in the field of ferroelectric materials. Contrary to Rochelle salt, KDP demonstrated the ability to maintain ferroelectric properties over a wide temperature range [32]. Nonetheless, similar to Rochelle salt, the initial applications of KDP were constrained due to both, material being fragile and water-soluble.

The discovery of ferroelectricity in Barium Titanate (BaTiO<sub>3</sub>, BTO) in the mid-20th century [33] marked the beginning of the "perovskite<sup>2</sup> era", which witnessed intensive research into perovskite materials. BTO became a model system for studying ferroelectric behaviour due to its robust properties including its ease of synthesis, water insolubility, chemical stability at room temperature, and superior electrical properties. Table 1.1 lists the properties of various oxide materials with perovskite or layered perovskite structures that exhibit ferroelectricity. The discovery of ferroelectricity in Lead Zirconate Titanate (Pb(Zr,Ti)O<sub>3</sub>, PZT) [34, 35] led to the development of ferroelectric random access memory (FeRAM) [36, 37] due to its superior ferroelectric properties that are largely independent of the crystalline quality of the material. FeRAM devices utilize the reversible polarization of ferroelectrics for data storage. In PZT, the electrical properties can be tuned for specific usage by adjusting the ratio of Zr and Ti atoms along with the donor and acceptor doping [38, 39]. The ferroelectric nature of PZT comes from the displacement of Zr or Ti elements within the perovskite structure. Despite its success, the high dielectric constant of  $\sim$  1300, coupled with a low coercive field and challenges in integrating it into CMOS process flows, complicates the scaling down of PZT-based ferroelectric devices below 90 nm thickness [40-42].

<sup>&</sup>lt;sup>2</sup>Perovskite is a crystal structure with the formula  $ABX_3$ , where A is a large cation (such as an alkali, alkaline earth, or rare earth metal), B is a smaller cation (often a transition metal), and X is typically oxygen.

|   | pted from [43].                                                 |

|---|-----------------------------------------------------------------|

|   | erties. Table adapted                                           |

|   | properties                                                      |

|   | es and their ]                                                  |

|   | kite structure.                                                 |

|   | vskite or layered perovskite structures and their properties. I |

| , | te or layer                                                     |

|   | vith perovski                                                   |

|   | c materials wit                                                 |

|   | electric ma                                                     |

|   | list of ferrc                                                   |

|   | able 1.1: A                                                     |

|   | Η                                                               |

|                                  | Chamiaal                                    | Voor       | Curie                      | Remnant                                            |                                                         |

|----------------------------------|---------------------------------------------|------------|----------------------------|----------------------------------------------------|---------------------------------------------------------|

| Compound                         | formula                                     | discovered | temperature $T_C$ (K)      | polarization,<br>$P_R$ ( $\mu$ C/cm <sup>2</sup> ) | Crystal structure                                       |

| Barium titanate                  | BaTiO <sub>3</sub>                          | 1945       | 398                        | 25                                                 | Tetragonal                                              |

| Potassium niobate                | KNbO <sub>3</sub>                           | 1949       | 400                        | 20-40                                              | Orthorhombic                                            |

| Lead zirconate titanate          | ${ m PbZr}_{1-x}{ m Ti}_x{ m O}_3$          | 1949       | Depends on the composition | 20-97                                              | Tetragonal for Ti-<br>rich, Rhombohedral<br>for Zr-rich |

| Lead titanate                    | $PbTiO_3$                                   | 1950       | 763                        | 20-96.5                                            | Tetragonal                                              |

| Lead zirconate                   | PbZrO <sub>3</sub>                          | 1951       | 503                        | 20-50                                              | Orthorhombic                                            |

| Lead bismuth niobate             | $PbBi_2Nb_2O_9$                             | 1959       | 833                        | ~3                                                 | Pseudo tetragonal                                       |

| Strontium bismuth tanta-<br>lite | ${ m SrBi}_2{ m Ta}_2{ m O}_9$              | 1960       | 600                        | 30-70                                              | Orthorhombic                                            |

| Barium strontium titanate        | $Ba_{0.73}Sr_{0.27}TiO_3$ 1960              | 1960       | 298                        | 10-30                                              | Tetragonal                                              |

| Bismuth titanate                 | $\mathrm{Bi}_4\mathrm{Ti}_3\mathrm{O}_{12}$ | 1961       | 953                        | 10-30                                              | Orthorhombic                                            |

The discovery of ferroelectricity in polyvinylidene fluoride (PVDF) in the 1980s introduced a new class of ferroelectric materials known as ferroelectric polymers [44, 45]. These materials combined flexibility with ferroelectric properties enabled applications in flexible electronics and enhanced the understanding of ferroelectric phenomena in such materials. These materials have been studied for their application in FeRAMs. Even though the flexible structure helps to overcome temperature instabilities, the long access time remains a disadvantage of this technology [46].

The 21<sup>st</sup> century has seen continued advancements with the emergence of multiferroics and two-dimensional ferroelectrics [47, 48]. In 2003, the discovery of roomtemperature multiferroicity in epitaxial bismuth ferrite (BiFeO<sub>3</sub>) thin films offered new ways to couple magnetic and electric properties, which proved to be crucial for nextgeneration computing and memory devices [49].

The discovery of ferroelectricity in Hafnia-based materials in 2011 [22] has attracted more attention to this field due to its ability to retain ferroelectricity even at ultra-thin dimensions allowing to overcome the scalability and CMOS-compatibility issues faced by the conventional perovskite-based ferroelectrics. Ferroelectric properties of Hafnia-based materials will be discussed in detail in the next section. Recently, the discovery of ferroelectricity in AlScN films [50] showed a high remnant polarization of 80-120  $\mu$ C/cm<sup>2</sup> [51]. However, this material has a much higher coercive field compared to Hafnia-based ferroelectrics, requiring higher voltages for polarization switching. Considering the mature deposition techniques and the CMOS compatibility of AlScN-based material, it shows great potential towards microelectronic applications. However this discovery is fairly recent and further study is required to reduce the leakage current and the coercive field of this material for practical applications.

### 1.1.3 Hafnium-oxide based ferroelectric thin films

The integration of non-ferroelectric  $HfO_2$  into CMOS processes was driven by its excellent properties as a high-k dielectric material, which helped to further miniaturize field effect transistor devices [52–54]. The discovery of ferroelectric properties in Si-doped  $HfO_2$  thin films introduced new possibilities for ferroelectric memory devices [22], as this material facilitated the scaling down and lowered the power requirement of ferroelectric devices - a challenge previously faced with traditional perovskite-based ferroelectric devices [55]. These advantages led to extensive research on this material in an attempt to enhance its properties to support the commercialization of ferroelectric memory devices.

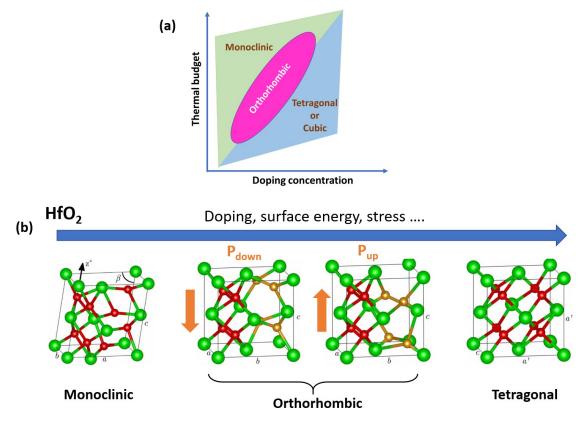

Figure 1.4: (a) Phase diagram of doped HfO<sub>2</sub>, adapted from [9]. (b) Schematic of the mechanisms and corresponding crystal phases (m-phase, o-phase and t-phase) stabilized in the HfO<sub>2</sub> thin films. In this representation, Hf atoms are depicted in green, oxygen atoms in red, and oxygen atoms that determine the polarization state are shown in golden colour. Depending on the position of the golden colour oxygen atoms, two polarization states  $P_{down}$  and  $P_{up}$  are obtained in the ferroelectric o-phase. In HZO films, Zr atoms occupy some cation sites instead of Hf atoms. This mixed occupancy stabilizes the orthorhombic phase, especially with specific doping levels and annealing processes. This figure is adapted from [32, 56].

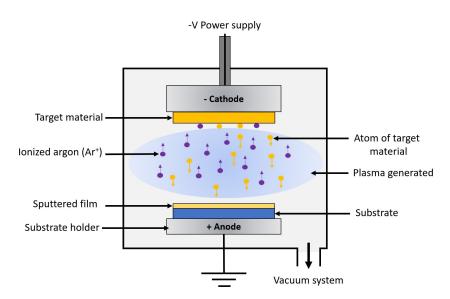

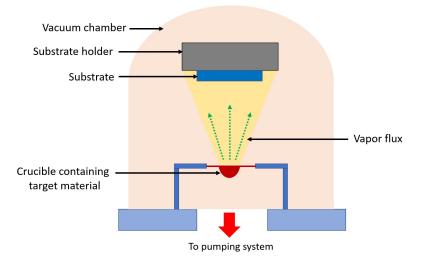

For hafnium oxide, achieving the ferroelectric phase necessitates thin films due to the structural constraints and stabilization mechanisms that occur at reduced dimensions. Ferroelectricity has been reported in HfO<sub>2</sub> thin films doped with many different elements such as Si, Zr, Y, Al, Gd, Sr, La, Ge and Sc [57–63]. Research also indicates that undoped HfO<sub>2</sub> thin films exhibit ferroelectric properties when oxygen vacancies are present in the film [56, 64]. The HfO<sub>2</sub> material is normally present in the stable monoclinic phase (mphase). At high temperatures and pressure, the tetragonal (t-phase) and cubic (c-phase) phases are stabilized in the material [55]. Neither of these phases gives rise to ferroelectricity. The ferroelectric behaviour in  $HfO_2$  films originates from the noncentrosymmetric orthorhombic phase (o-phase, space group Pca2<sub>1</sub>) [55]. This phase is not found in the equilibrium phase diagram of  $HfO_2$ . It is possible to stabilize this polar phase by tuning the amount of oxygen vacancies [65], controlled doping of different elements [57], rapid quenching [66] and mechanical stress [55]. However, it is difficult to study the impact of each of these factors independently as these factors usually coexist.

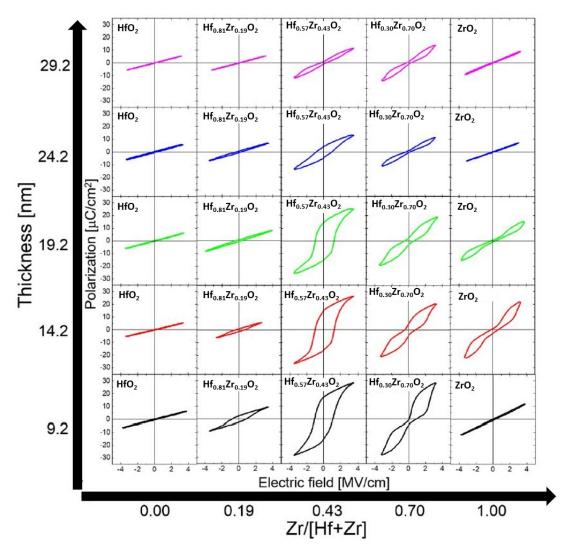

Figure 1.5: Polarization-electric field (P-E) curves for  $Hf_{1-x}Zr_xO_2$  films with varying compositions and thicknesses. The top and bottom electrodes were made of Pt/TiN (with the TiN layer in contact with the dielectric) and TiN, respectively. All the tested capacitor samples were annealed at 500 °C in a nitrogen atmosphere for 30 seconds following the top electrode deposition. Figure adapted from [67].

When the oxygen supply during the deposition (physical vapour deposition (PVD) or atomic layer deposition (ALD) deposition) of  $HfO_2$  film (10 nm) is reduced, it leads to the

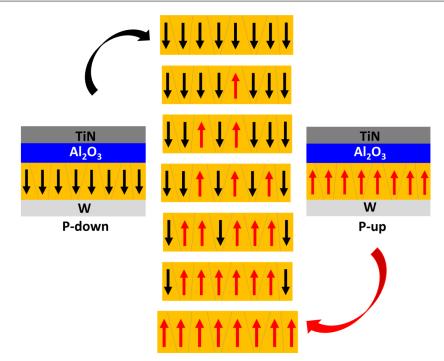

generation of oxygen vacancies stabilizing the o-phase. Further increase in the amount of oxygen vacancies leads to the stabilization of the t-phase [65]. The phase diagram corresponding to the solid solution of  $HfO_2$  film is shown in Figure 1.4(a). The dopant concentration required to stabilize the o-phase depends on dopants. Generally, the gradual increase in the dopant concentration leads to a decrease in m-phase and stabilizes the ophase. Further increase in the dopant concentration leads to the stabilization of t-phase or c-phase [41]. In the ferroelectric o-phase of  $HfO_2$ , the oxygen atoms can occupy two stable positions, shifting up or down in response to the polarity of an externally applied electric field. Depending on the orientation of these oxygen atoms, a permanent electric dipole is established that can point either upwards ( $P_{up}$ ) or downwards ( $P_{down}$ ) as shown in Figure 1.4(b).

Among the different dopants used for attaining stable o-phase in the Hafnia-based thin film, Zr is the most promising [55].  $Hf_{1-x}Zr_xO_2$  thin films show ferroelectric properties for a wide range of doping concentrations, making the process very flexible [67]. Hf and Zr share very similar physical and chemical properties. As a result, the optimal doping concentration of Zr to achieve the highest remnant polarization is around 50% (shown in Figure 1.5 for different film thicknesses), while for other dopants (e.g., La), a significantly lower concentration is required to attain similar effects [23, 61, 68]. Hence, obtaining homogenous and reproducible ferroelectric thin films with Hf:Zr ratio of 1:1 is relatively easy compared to other ratios required for different dopants using atomic layer deposition (ALD) technique. This is due to the vertical inhomogenous doping effect in ALD [55]. From Figure 1.5, it is clear that  $Hf_{1-x}Zr_xO_2$  films show ferroelectric properties when  $x \sim 0.5$  due to the stabilization of o-phase even at a smaller thickness of 9.2 nm. As the Zr compositional ratio (x) increases from 0 to 1, the film starts to show nonlinear dielectric properties for film thicknesses of 9.2 nm to 29.2 nm. When the x value is in the range of 0.3 to 0.5, the film shows ferroelectric behaviour and when it is in the range of 0.7 to 1, the film shows antiferroelectric-like behaviour [55]. Hf-rich films crystallize in the m-phase, whereas Zr-rich films crystallize in the t-phase. This trend has been reported in many studies [55, 69]. The  $Hf_{0.5}Zr_{0.5}O_2$  (HZO) thin films can be crystallized in ferroelectric o-phase at a relatively lower processing temperature ( $\sim 400$  °C) [70], whereas the other dopants require much higher heat treatment (>  $650 \degree C$ ) for stabilizing

the o-phase [55, 68]. This characteristic allows ferroelectric HZO to be compatible with the CMOS back-end-of-line.

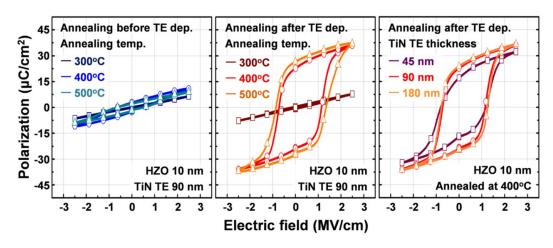

Figure 1.6: P-E hysteresis curve from TiN-HZO(10 nm)-TiN stack after wake-up of  $10^5$  cycles (wake-up cycling with 2.5 MV/cm) annealed at 300 °C to 500 °C before and after TiN top electrode deposition. Figure reproduced from [71].

The HZO films crystallize between the bottom and top electrodes, which apply mechanical stress to the HZO film, influencing the stabilization of the ferroelectric o-phase. As shown in Figure 1.6, 10 nm HZO film crystallized with the presence of TiN top electrode showed higher remnant polarization compared to the HZO film crystallized in the absence of TiN top electrode at different annealing temperatures ranging from 300 °C to 500 °C. This was because the crystallization of HZO in the absence of TiN top electrode was leading to the formation of o-phase along with m-phase in the film. Whereas when the film was crystallized with the TiN top electrode, o-phase with crystallographic orientation along (111) plane was obtained [71]. The thickness of the TiN top electrode also influenced the ferroelectric nature of the HZO thin film. An increase in TiN top electrode thickness also increases the o-phase ratio in HZO [55]. Researchers have extensively studied the role of different electrodes and their thicknesses on the ferroelectric properties of HZO films by providing the mechanical stress needed to stabilize the o-phase [72–75]. The mechanical stress is imparted to the film through the engineering of the capping layer or by adjusting the thermal expansion coefficient of the substrate based on the choice of electrodes, which affect the orientation and grain size of the HZO films [71, 76–82]. It is well established that the use of TiN top electrode (a favoured material for mass production) provides tensile stress to the HZO film during annealing, which helps in the

stabilization of o-phase [71, 72, 79].

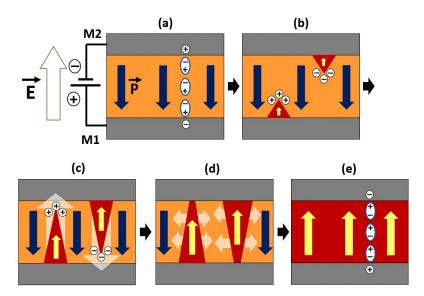

#### **1.1.4** Models of polarization switching mechanisms

Polarization switching in ferroelectric materials is a complex process characterized by the formation and growth of domains within the material ([83], see Figure 1.7(a)-(e)). This process is critical for the functioning of ferroelectric devices. Polarization switching can be initiated by applying an external voltage, which reorients the dipoles in the ferroelectric material, resulting in a change in its polarization state. The dynamics of this process can be described through various theoretical models, each providing insights into different aspects of domain behaviour and switching kinetics. Understanding models of polarization switching mechanisms is crucial as it provides insights into the fundamental behaviours of ferroelectric materials used in ferroelectric memory devices.

Figure 1.7: Schematic of polarization switching process under an applied electric field E [83]. (a) Initially, the polarization is fully oriented downwards. (b) Upon exceeding a certain voltage threshold, nucleation of a flipped domain begins. (c) Driven by charges at the domain wall, the flipped domain rapidly propagates. (d) As polarization aligns mostly parallel to the domain wall, a more energetically stable state is achieved, resulting in slow lateral growth. (e) The domain is fully switched.

#### Merz's law

Merz's law is a fundamental relation that describes the correlation between the switching time ( $\tau$ ) and the applied electric field (E) [84]. According to this law, the switching time

is exponentially related to the activation field (E<sub>a</sub>) required for polarization reversal:

$$\tau = \tau_0 \cdot \exp\left(\frac{E_a}{E}\right) \tag{1.4}$$

where  $\tau_0$  is the intrinsic switching time. Notably,  $E_a$  is temperature-dependent. This relationship indicates that films with a higher activation field will require a longer time to switch their polarization state for a given applied field. However, Merz's law does not provide a detailed mechanism for the switching process, prompting the development of more sophisticated models.

#### Kolmogorov-Avrami-Ishibashi (KAI) model

In this model, domain nucleation occurs instantaneously throughout the material [85]. Once nucleated, domain walls move horizontally, causing the domain to expand until it encounters another domain wall [86]. The time-dependent polarization change ( $\Delta$  P(t)) in this model is given by:

$$\Delta P(t) = 2P_s [1 - \exp(-\left(\frac{t}{\tau}\right)^n], \qquad (1.5)$$

where  $P_s$  is the spontaneous polarization and n is an effective dimensionality factor. Here,  $\tau$  is the total switching time. This model suggests that domain expansion is the most time consuming aspect of polarization switching. KAI model is commonly applied to describe the behaviour of traditional single-crystal perovskite ferroelectrics [87, 88] and epitaxial thin film ferroelectrics [89]. However, this model fails to accurately describe the domain reversal behaviour in polycrystalline ferroelectric thin films, particularly at low applied fields [90–92].

#### Nucleation-limited switching (NLS) model

In thin  $HfO_2$ -based ferroelectric films, which typically exhibit a polycrystalline structure, the nucleation-limited switching (NLS) model provides a more accurate description. Due to the presence of multiple grains and potential defects, domain propagation is limited, leading to numerous nucleation events with small nuclei sizes [92–94]. These nucleation sites can include grain boundaries, interfaces, and impurities. The NLS model suggests

that many nucleation events occur simultaneously, and the growth rate of these nuclei depends on both volume and surface energy contributions. The switching field is assumed to be proportional to the coercive field ( $E_C$ ), and the relationship between the coercive field and the ferroelectric layer thickness ( $d_{FE}$ ) is given by [95]:

$$E_{\rm C} \propto d_{\rm FE}^{-2/3} \tag{1.6}$$

This relationship holds until a saturation plateau is reached, beyond which  $E_C$  becomes independent of layer thickness and is instead determined by grain size. The KAI model treats the switching time  $\tau$  as a constant fitting parameter, while the NLS model proposes that the switching time follows a Lorentzian distribution. For the NLS model, the timedependent polarization switching is formulated as [96],

$$\Delta P(t) = 2P_s \int \left[1 - \exp(-\left(\frac{t}{\tau}\right)^n\right] F(\log\tau) \, d(\log\tau), \tag{1.7}$$

where

$$F(\log \tau) = \frac{A}{\pi} \left( \frac{\omega}{(\log \tau - \log \tau_1)^2 + \omega^2} \right).$$

(1.8)

Here A is the normalized constant,  $\omega$  is the half-width at half-maximum of the distribution and  $\log(\tau_1)$  is the median logarithmic value of the distribution. According to this model, nucleation events dominate the polarization switching kinetics. This model is extensively used in the literature to describe polarization reversal in both traditional perovskites and HfO<sub>2</sub>-based films [93, 97–99].

#### Landau-Devonshire theory

From a thermodynamic perspective, the Landau-Devonshire theory provides a macroscopic description of polarization switching [100]. It considers the free energy landscape of a ferroelectric material, where two energy minima correspond to the two stable polarization states. An external electric field is required to overcome the energy barrier between these states. This theory assumes that the coercive field is intrinsic and independent of the switching duration, which contrasts with experimental observations showing a time-voltage correlation [41]. To reconcile these discrepancies, the multi-grain Landau-Khalatnikov approach was developed for  $HfO_2$ -based ferroelectrics [101]. This approach incorporates a time-dependence by considering a distribution of local fields averaged over multiple regions within the ferroelectric film. This model accounts for the macroscopic behaviour of polarization switching in polycrystalline materials.

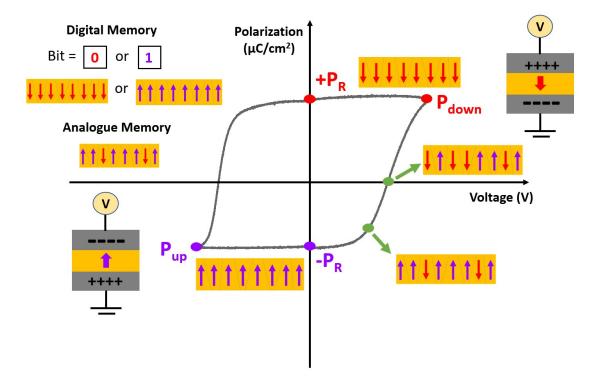

# 1.1.5 Ferroelectricity for memory applications

In ferroelectric materials, the spontaneous polarization can be reversed by applying an external electric field. When an electric field of sufficient magnitude is applied in the direction opposite to the initial polarization, the domains within the ferroelectric material realign to switch the polarization direction. This switching mechanism is highly stable and non-volatile, meaning the polarization state remains even after the electric field is removed. As shown in Figure 1.8, this bistability forms the basis of binary memory devices, where the two polarization states are used to encode binary information.

Figure 1.8: Schematic representation of utilizing ferroelectric properties for binary and analog memory applications. Aligning all dipoles in the down or up direction facilitates binary data storage as '0' or '1' bits. In contrast, applying a lower magnitude electric field achieves partial domain switching, enabling analog memory applications.

The ferroelectric domain switching is not always an all-or-nothing process. When a lower magnitude electric field is applied, it can cause partial switching of domains, leading to intermediate polarization states. This partial or gradual switching is a result of the complex interplay between different domains within the ferroelectric material. By precisely controlling the applied electric field, it is possible to achieve a range of stable polarization states between the fully polarized  $P_{up}$  and  $P_{down}$  states. Ferroelectric memory devices utilize this gradual switching capability to store data in a continuous manner. Instead of representing data as a simple 0 or 1 (binary form), these memories can store a range of values, leading to multiple resistance states. This is particularly useful in applications such as neuromorphic computing and in high-resolution data storage solutions. There are three types of ferroelectric memory devices that utilize ferroelectric materials for data storage. While they share similarities in their programming principles, they differ in their structures and working mechanisms.

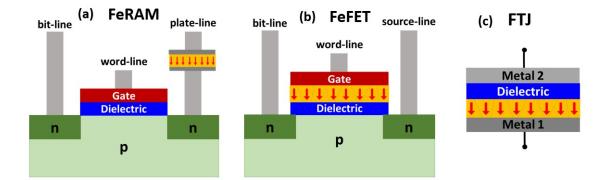

Figure 1.9: Schematic representation of (a)1T–1C FeRAM device, (b) FeFET device and (c) FTJ device.

• Ferroelectric random access memory (FeRAM): In FeRAM, each memory cell consists of a ferroelectric capacitor paired with a transistor as shown in Figure 1.9(a). This type of architecture is called 1T-1C memory cell. In FeRAMs, the data is stored in the ferroelectric capacitor and the transistor connected to it acts as a switch. The two different polarization states of the ferroelectric materials can be used within a capacitor to create two states for a memory cell. The read operation of FeRAM involves a sequence of stages, closely resembling the process used in DRAM. Initially, the memory cell is in an inactive state with the bit line, plate line, and word line all set to low. To initiate the read operation, voltages are applied to the word line and plate line. This places an electric field across the ferroelectric capacitor, causing it to either switch or remain in its current state, depending on the stored data. If the capacitor switches, it induces a charge that is shared with

the bit line capacitance. The resulting bit line voltage is proportional to the ratio of the switched capacitance ( $C_s$ ) to the bit line capacitance ( $C_{bit}$ ). This voltage is then compared to a reference voltage using a sense amplifier, which amplifies the difference to determine whether the stored bit is a logic '0' or '1'. Since reading the cell can alter its state, FeRAM employs a process to restore the original data immediately after the read operation, ensuring data integrity.

The write operation in FeRAM also leverages the unique properties of ferroelectric materials. To write data, the control circuitry applies a field across the ferroelectric capacitor in the desired direction, switching its polarization state to represent either a binary '0' or '1'. This data remains intact even when power is removed due to the non-volatile nature of ferroelectric materials. Unlike DRAM, where the charge gradually leaks away, the polarization state in FeRAM does not degrade over time, providing indefinite data retention. The first demonstration of non-volatile DRAM (FeRAM) was done recently [102]. It has just begun to be shown in high densities as a commercial DRAM technology.

• Ferroelectric field effect transistor (FeFET): The FeFET consists of a 1T memory cell. Its structure includes a source and bit line, a gate electrode, and a ferroelectric layer sandwiched between the gate electrode and the channel, as shown in Figure 1.9(b). This ferroelectric layer exhibits stable polarization states that can be reversed by an external electric field.

The writing process in FeFETs involves setting the polarization state of the ferroelectric layer to store data. This is done by applying a voltage to the gate while grounding the bulk, with the source and drain either floating or at a fixed potential. This ensures effective polarization switching without interference from current flow through the source and drain. If the desired data bit is a logic '1', a positive voltage is applied to the gate, causing the electric field to align the dipoles in the ferroelectric material in one direction. Conversely, if the desired data bit is a logic '0', a negative voltage is applied, aligning the dipoles in the opposite direction. This alignment of dipoles creates a corresponding electric field within the ferroelectric layer, which modulates the threshold voltage of the transistor. The polarization state remains stable even after the removal of the applied voltage due to the non-volatile nature of the ferroelectric material. This ensures that the data is retained without the need for a continuous power supply.

The read operation in FeFETs involves identifying the current through the transistor and associating it with a state of polarization to retrieve the stored data. During a read operation, a small voltage is applied between the source and drain terminals of the transistor and the gate voltage is set to a level that allows the transistor to either conduct or remain non-conductive based on the polarization state. If the ferroelectric layer's polarization corresponds to a logic '1', the transistor's threshold voltage is altered in a way that allows current to flow through the channel. If the polarization corresponds to a logic '0', the threshold voltage remains high, preventing current flow.

The critical aspect of the FeFET read mechanism is that it is non-destructive, that is, the polarization state of the ferroelectric material is not altered during the read process. This ensures that the data remains intact and can be read multiple times without degradation. The FeFET concept faces notable retention challenges due to charge trapping and depolarization field effects at the dielectric interface between the ferroelectric layer and the semiconductor channel. These retention issues compromise the reliability of FeFETs and must be resolved to facilitate the successful commercial integration of 1T cells. However, recent advancements have shown that FeFETs can achieve multiple resistance states through cumulative switching [103]. This breakthrough opens up new possibilities for FeFETs in neuromorphic computing and logic-in-memory applications, significantly increasing interest in these devices.

• Ferroelectric tunnel junction (FTJ): FTJs utilize the unique properties of ferroelectric materials and quantum tunneling to store data. An FTJ device consists of a ferroelectric layer or a combination of ferroelectric and dielectric layers sandwiched between two metallic electrodes, creating a capacitor-like structure as shown in 1.9(c). The polarization of the ferroelectric layer controls the FTJ device's tunneling current. High resistance at a specific read voltage indicates logic '0', and low resistance indicates logic '1'. Data writing is accomplished by switching the polarization of the ferroelectric layer to either the up or down direction, while reading is performed by measuring the current flowing through the stack at a voltage smaller than the positive or negative coercive voltage.

FTJs offer several advantages over other ferroelectric memory technologies such as FeRAM and FeFETs. Compared to FeRAM, FTJs are superior due to their nondestructive readout mechanism and enhanced scalability, enabling higher memory density and a reduced physical footprint. FTJs outperform FeFETs with their simpler two-terminal structure, which reduces fabrication complexity. Additionally, FTJs exhibit lower power consumption, better retention, and superior endurance properties. They also feature fast switching speeds, making them suitable for highspeed, energy-efficient applications. FTJs can achieve multilevel cell capability by storing multiple bits per cell through intermediate resistance states, further enhancing storage density. Their straightforward fabrication process is compatible with existing semiconductor manufacturing techniques, facilitating easier integration into current technology nodes. This thesis focuses on FTJ memory devices and their working mechanisms which will be discussed in detail in the following section.

# **1.2** Ferroelectric tunnel junction (FTJ)

A typical FTJ consists of two metal layers separated by a thin ferroelectric insulating barrier, see Figure 1.9(c). Although classically forbidden, electrons can traverse this potential barrier if its height exceeds the electron's energy through quantum mechanical tunnelling. The profile of the ferroelectric potential barrier depends on the direction of polarization in the ferroelectric layer, resulting in different tunnel resistances for the two polarization directions. However, the tunnelling probability becomes significant only when the barrier is ultrathin, typically just a few nanometers thick. The concept of FTJs was first introduced by Esaki et al. in 1971 [104], who predicted a change in tunnel resistance upon ferroelectric polarization switching. Achieving this goal presents significant challenges, primarily because it necessitates the creation of ultrathin films that retain strong ferroelectric properties at thicknesses of only a few unit cells. It was not until the early 2000s that substantial progress was made. In 2005, Kohlstedt et al. [105] and Zhuravlev et al. [106]

conducted theoretical investigations into the current-voltage characteristics of FTJs, providing a crucial understanding of their behaviour. Following this, in 2006, Tsymbal and Kohlstedt proposed mechanisms contributing to resistance changes, enhancing the theoretical framework for FTJs [107].

The first experimental demonstration of FTJs using multiferroic barriers was achieved by Gajek et al. in 2007 with  $La_{0.1}Bi_{0.9}MnO_3$  (LBMO) films [108]. This was followed by significant experimental advancements in 2009 and 2010, when Gruverman and Crassous demonstrated FTJs using BaTiO<sub>3</sub> [109] and PbTiO<sub>3</sub> [110], respectively. In 2009, Garcia demonstrated the non-destructive readout of ferroelectric states on an FTJ device based on a highly strained BaTiO<sub>3</sub> ultrathin film (3nm thick), which is a critical feature for practical memory devices [111].

A pivotal moment came in 2014 when Li et al. reported the first epitaxial FTJ on silicon [112]. This breakthrough demonstrated the potential for integrating FTJs with existing silicon technology, a crucial step for their application in conventional semiconductor processes. In 2015, Guo further demonstrated functional FTJ devices on silicon with good performance, underscoring the practical viability of FTJ technology [113]. However, integrating FTJs with ultrathin perovskite ferroelectric films into conventional silicon-based memory technology faces several challenges, such as poor interfacing with silicon, high crystallization temperatures, and electrical degradation from forming gas treatments [114]. HfO<sub>2</sub>-based ferroelectric materials offer a solution to these issues. In 2017, Ambriz-Vargas et al. successfully fabricated an FTJ using a CMOS-compatible  $Hf_{0.5}Zr_{0.5}O_2$  tunnel barrier on a TiN electrode, demonstrating its potential for seamless integration into silicon-based memory technologies [115]. In the same year, research by Boyn et.al on solid-state synaptic learning based on FTJs with BiFeO<sub>3</sub> as a ferroelectric layer, demonstrated its potential for neuromorphic computing applications, where they could mimic synaptic activities of the human brain [116]. This was further advanced in 2018 by Guo et.al, who demonstrated synaptic learning in FTJs based on BaTiO<sub>3</sub>, solidifying its role in advanced computational architectures [117]. This work also demonstrated that interface plays a vital role in the functioning of FTJs. Through interface engineering once can adjust the intrinsic band alignment of the ferroelectric/metal-semiconductor heterostructure, resulting in varied resistive switching processes. In 2019, Kobayashi et al. demonstrated multi-level operation on FTJ devices using a 4 nm thick ferroelectric HZO layer [118].

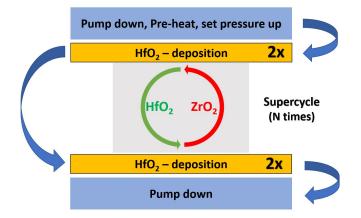

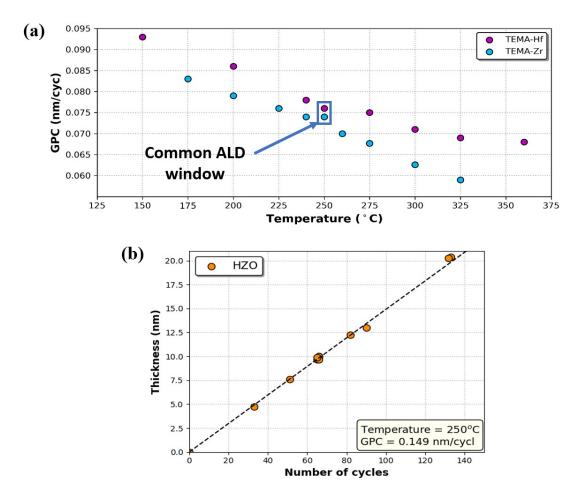

As previously mentioned, achieving high remnant polarization at a small thickness (1-4 nm), a requirement for high performing FTJ device, is challenging and as an alternative, a new device architecture was demonstrated by Max et.al in 2019 with HZO ferroelectric layer and Al<sub>2</sub>O<sub>3</sub> dielectric layer [119]. Instead of using a metal-ferroelectric-metal (M-FE-M) stack, it used a metal-ferroelectric-dielectric-metal (M-FE-DE-M) architecture. The novelty of this type of stack was first proposed and proven by Meyer et.al in 2004 as a ferroresistive RAM [120]. In this case, the HZO ferroelectric layer serves as the memory layer, where the information is stored as the polarization state and the dielectric layer serves as the tunnelling barrier for electron conduction. This study highlighted the direct correlation between memory properties and phenomena such as wake-up and fatigue in the ferroelectric layer and suggested that optimizing the ferroelectric/dielectric interface could improve the viability of FTJs for memory applications. In the same year, Ryu et al. demonstrated that FTJ devices based on an HZO ferroelectric layer with an M-FE-DE-M architecture could be used for neuromorphic applications [121]. They achieved multiple resistance states through pulse modification, showcasing the potential of these devices for advanced computing applications.

Despite these advancements, there are still challenges to be addressed for the commercial viability of Hafnia-based FTJ devices. Key issues include improving the reliability and endurance of the devices, ensuring uniformity in large-scale production, and further integrating FTJs with existing semiconductor technologies. Continued research and development are expected to overcome these challenges, paving the way for FTJs to become a standard component in high-density memory storage and neuromorphic computing applications. This thesis work began in January 2020, aiming to develop FTJ devices with an HZO ferroelectric layer and integrate them into the CMOS back end of line with application to neuromorphic computing.

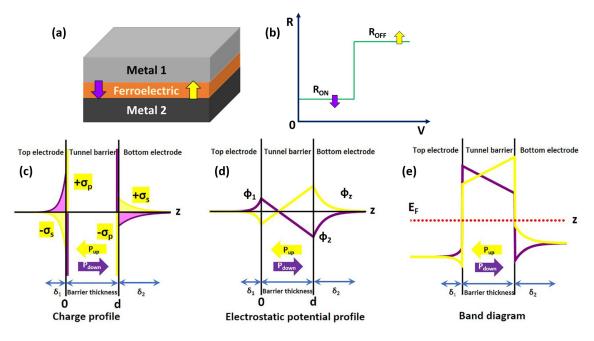

# **1.2.1** Physics of FTJ devices

In its very simple form, an FTJ device consists of a ferroelectric layer located between two dissimilar metal electrodes as shown in Figure 1.10(a). The two polarization directions of

the ferroelectric layer leads to two different resistance states as shown in Figure 1.10(b). This phenomenon is known as the tunnelling electroresistance (TER) effect [122]. The screening length refers to the distance within a metal over which mobile charge carriers (electrons) can neutralize the electric field caused by an external charge. It is a measure of how effectively a metal can screen or mitigate the electric fields emanating from the ferroelectric layer. The two metal electrodes (Metal 1 and Metal 2) have a different screening lengths ( $\delta_1$  and  $\delta_2$ ). The polarization charges are screened by the screening charges per unit area ( $\sigma_s$ ), shown in Figure 1.10(c). According to Thomas-Fermi model, this can de defined as,

$$\sigma_{\rm s} = \frac{\rm Pd}{\epsilon_{\rm b} \left(\frac{\delta_1}{\epsilon_1} + \frac{\delta_2}{\epsilon_2}\right) + \rm d},\tag{1.9}$$

where P is the ferroelectric polarization, d is the ferroelectric thickness,  $\epsilon_1$ ,  $\epsilon_2$  and  $\epsilon_b$  are the static dielectric constants of Metal 1, Metal 2 and barrier, respectively [123].

Figure 1.10: Schematic of (a) the FTJ structure and (b) the two resistance states  $R_{OFF}$  and  $R_{ON}$  of FTJs through polarization switching. (c) Charge distribution, (d) the corresponding electrostatic potential profile, and (e) the band diagram of an M1-FE-M2 FTJ with different polarization directions. It is assumed that the screening length of metal 1 is shorter than that of metal 2, resulting in an asymmetry in the potential profile. Yellow and purple colours indicate different polarization directions. Figure adapted from [123].

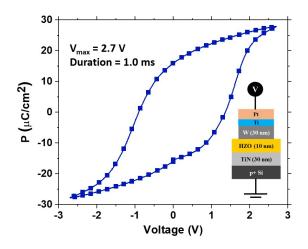

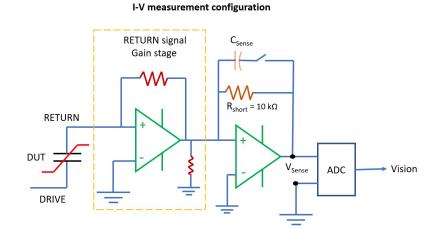

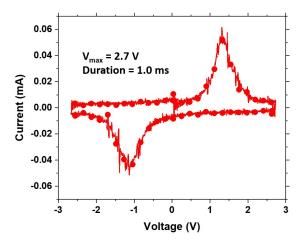

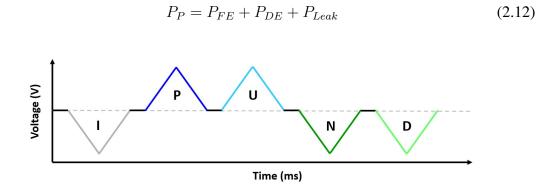

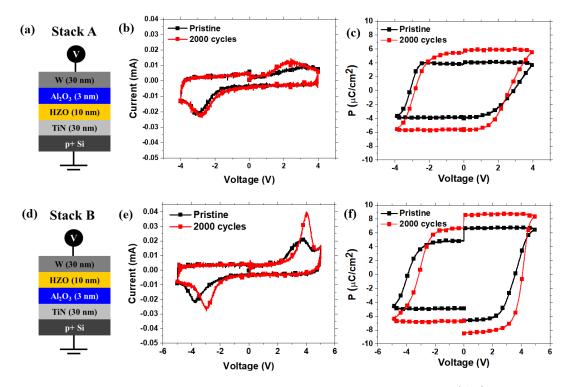

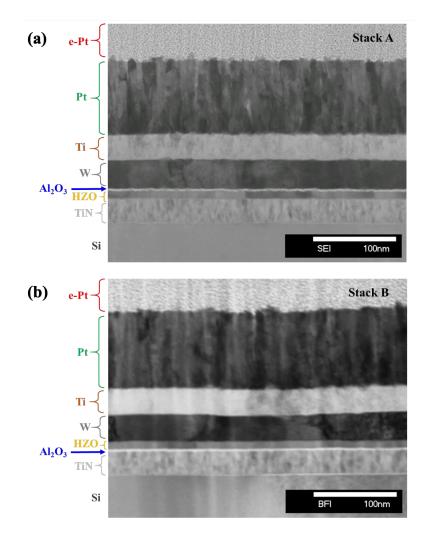

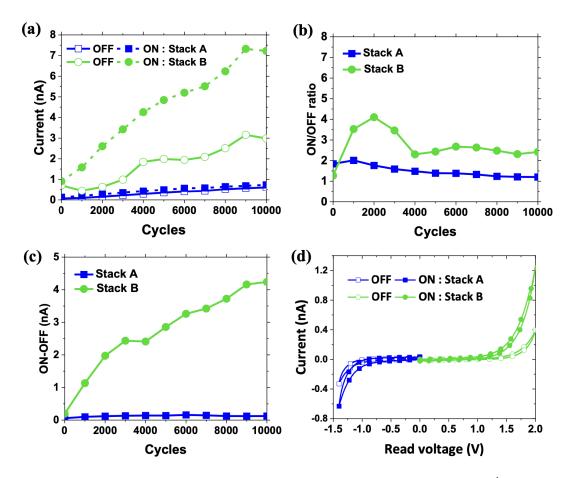

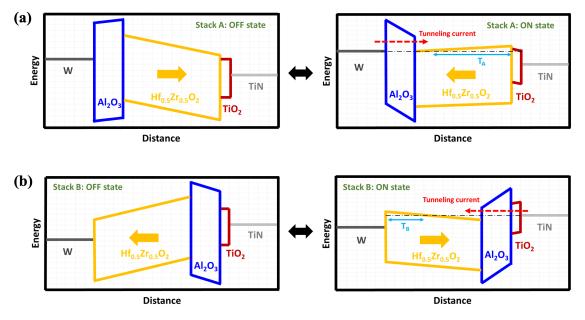

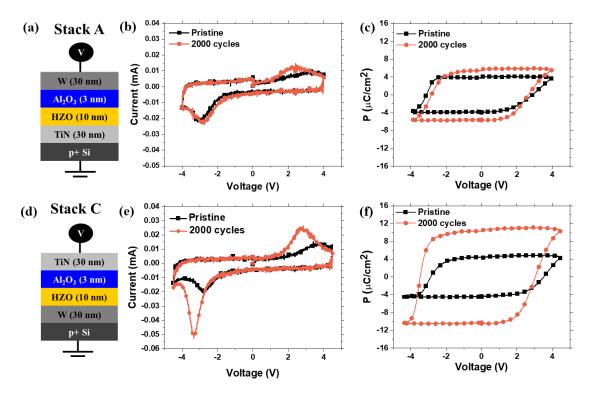

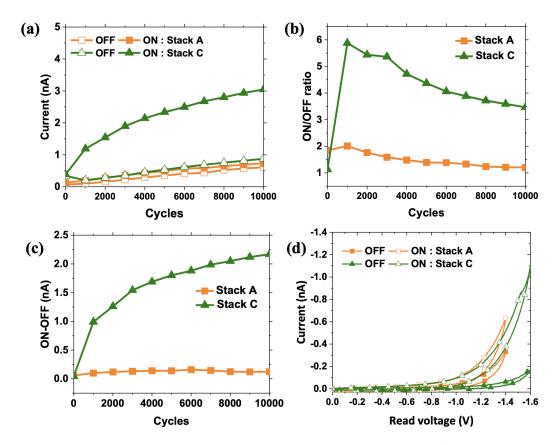

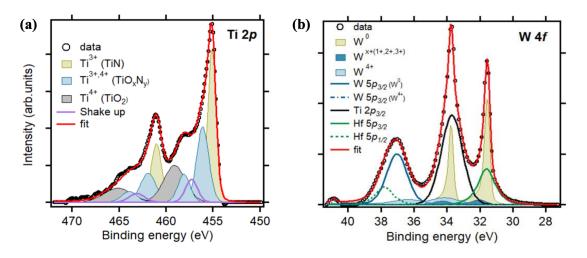

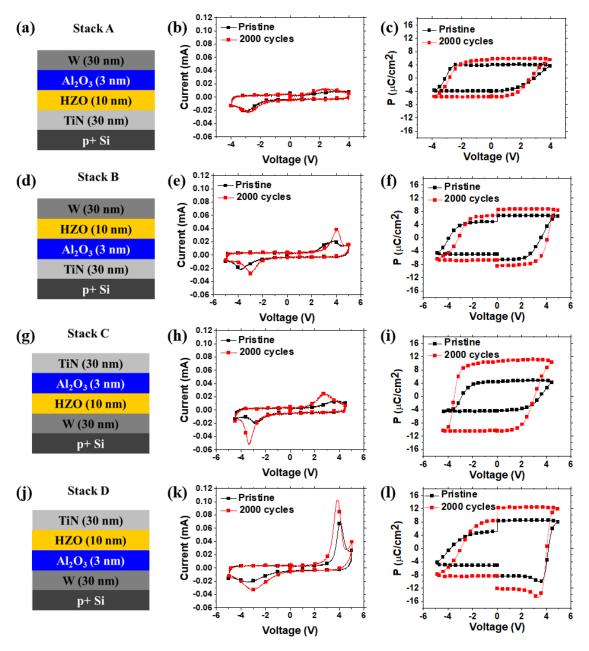

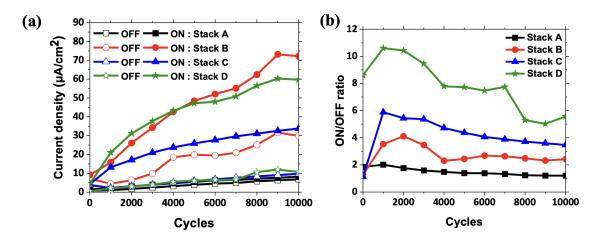

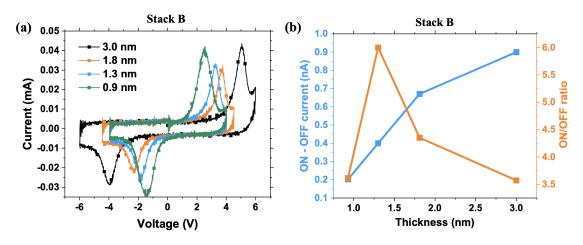

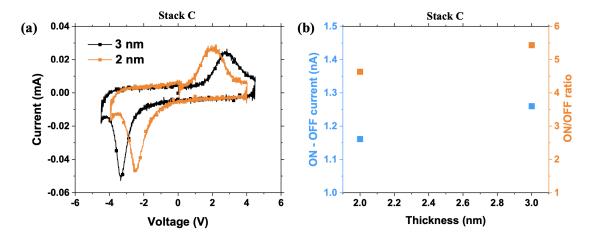

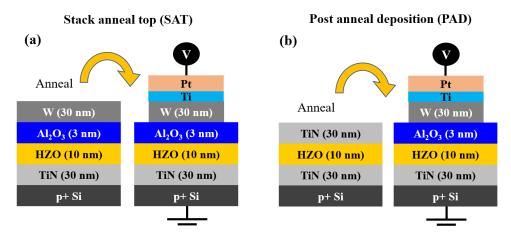

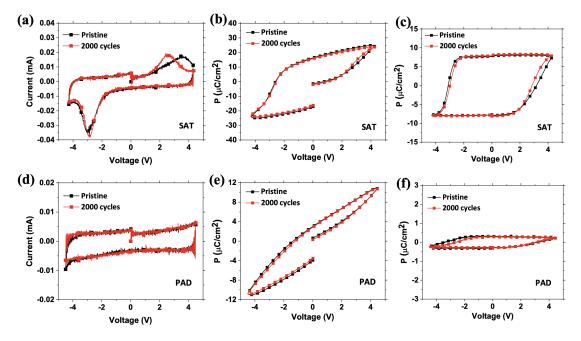

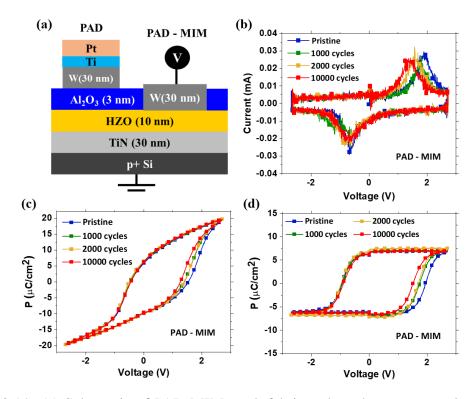

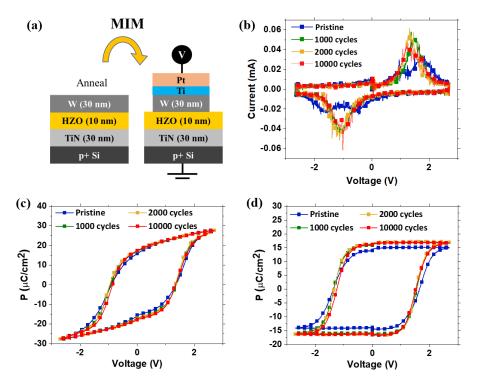

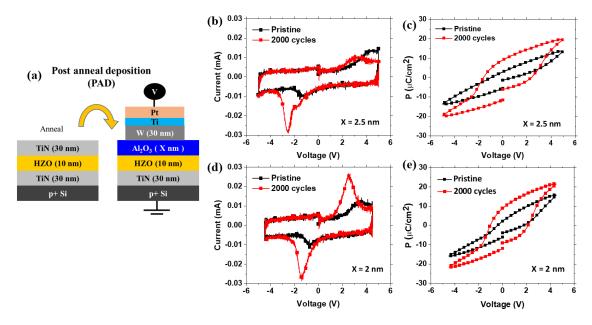

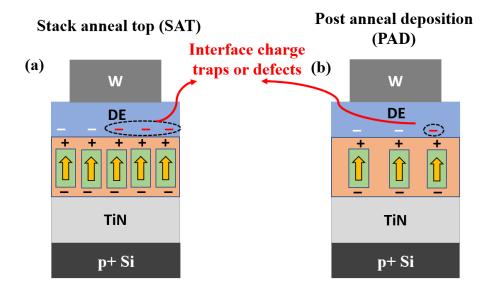

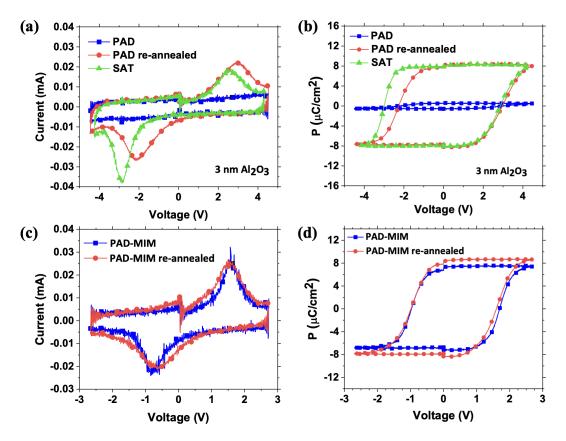

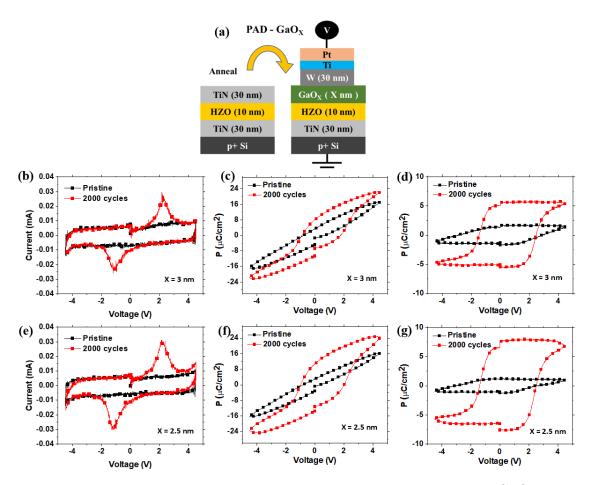

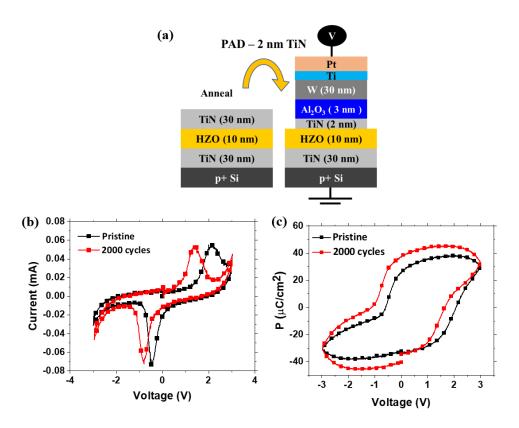

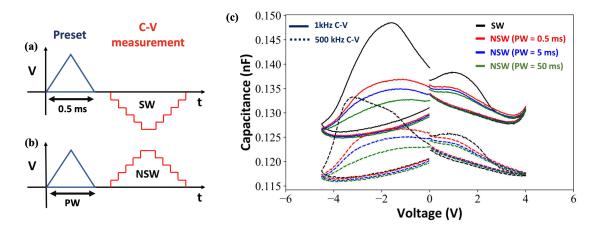

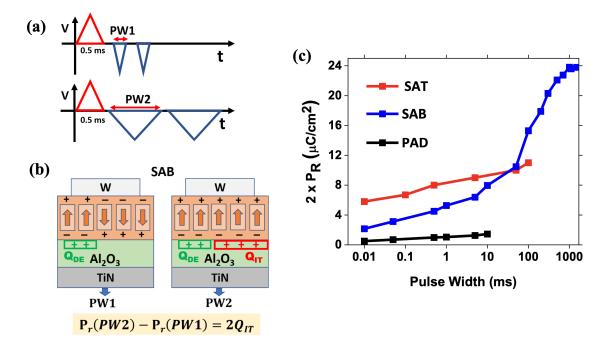

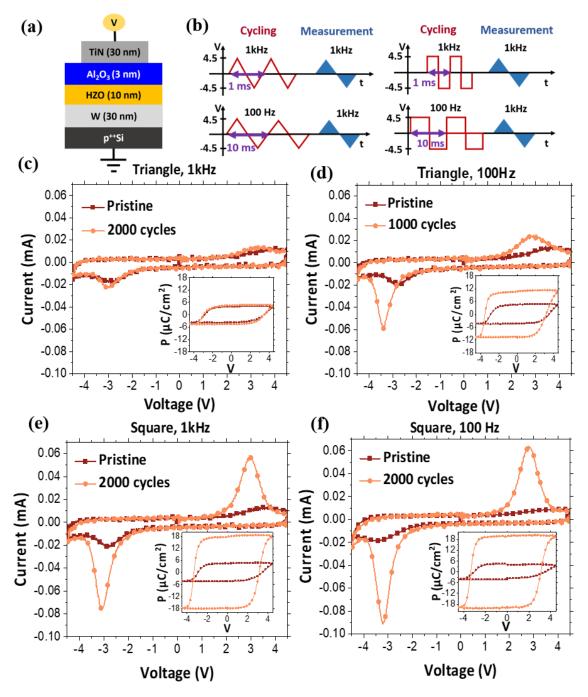

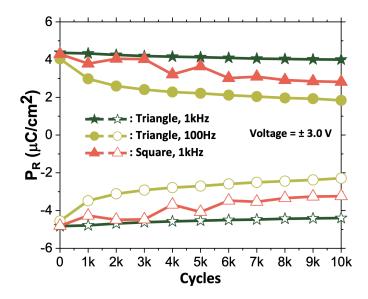

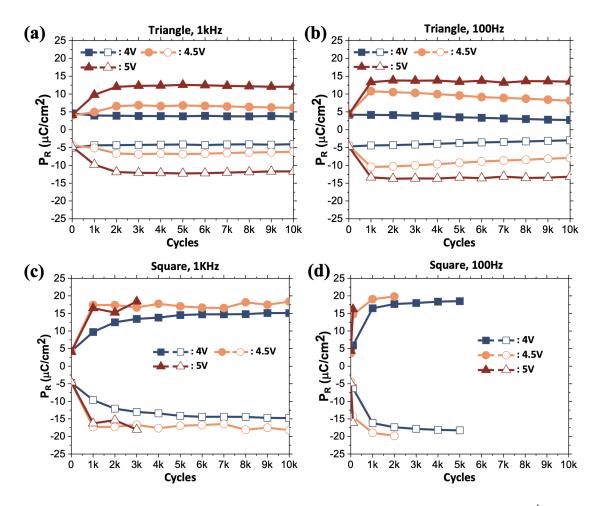

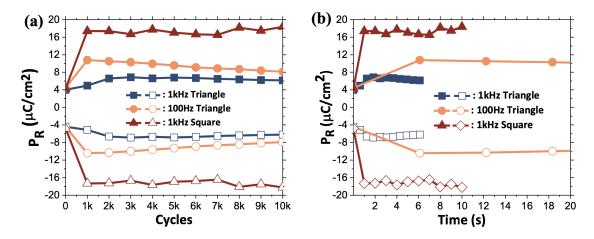

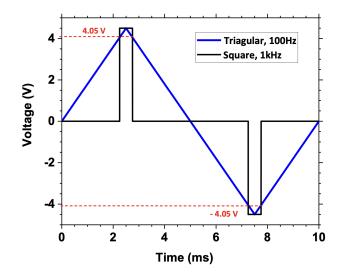

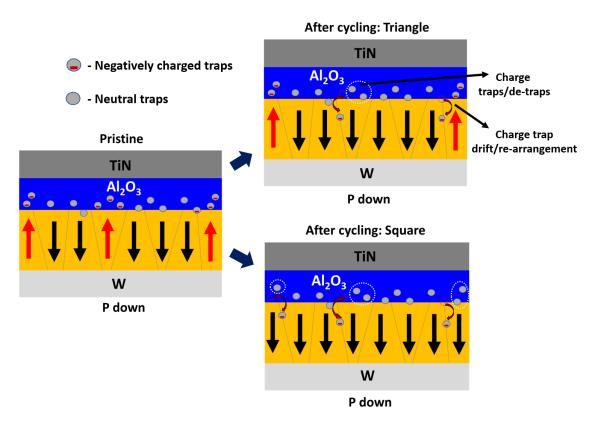

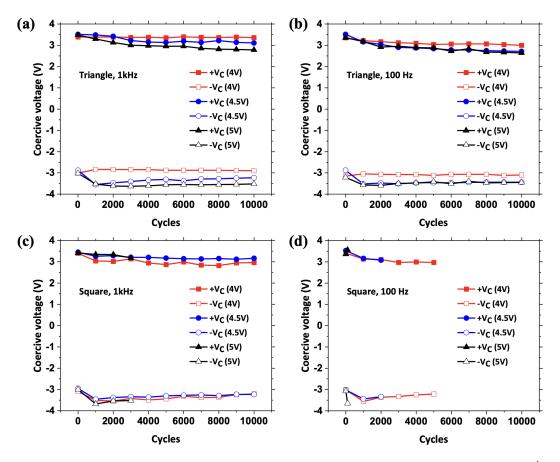

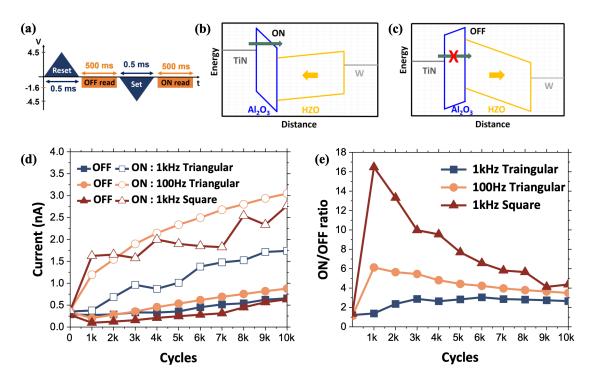

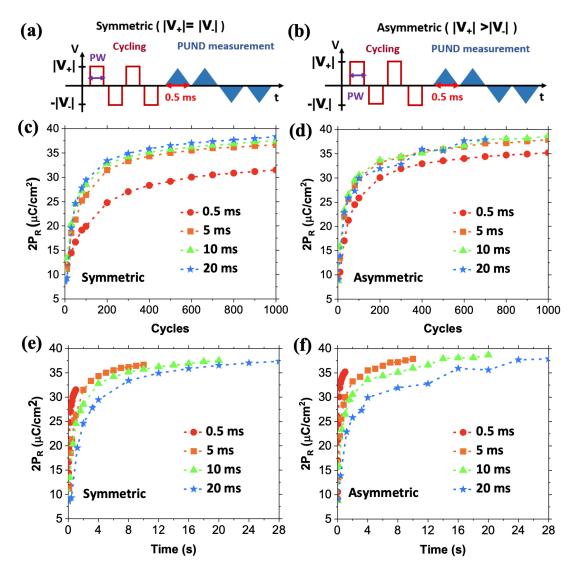

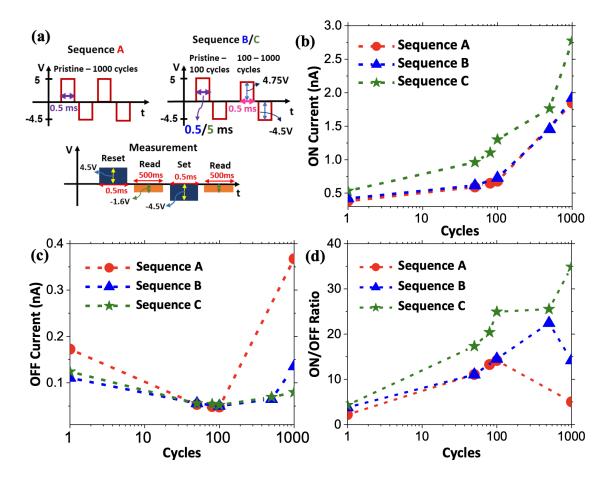

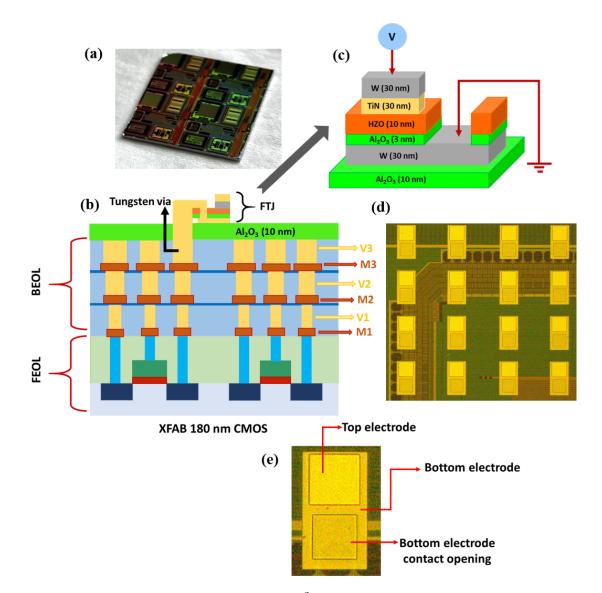

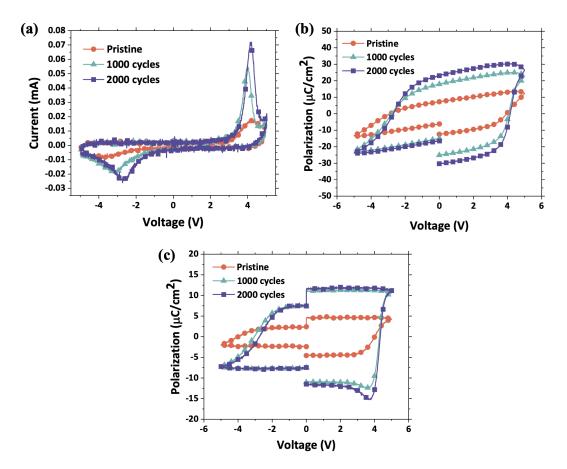

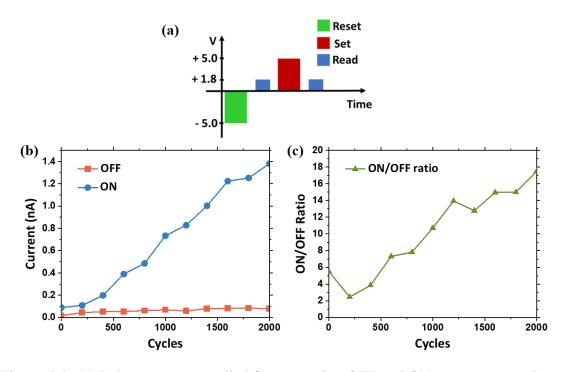

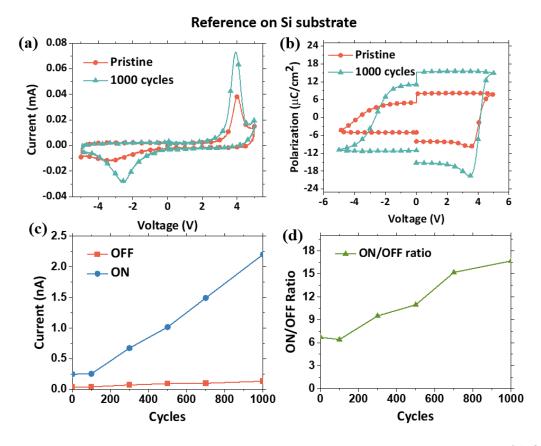

Due to the incomplete screening of the bound charges, an electrostatic potential ( $\phi(z)$ ) arises within the M-FE-M stack as shown in Figure 1.10(d) and it can be defined as,