Contents lists available at ScienceDirect

Solid State Electronics

journal homepage: www.elsevier.com/locate/sse

# Amorphous $GaO_x$ based charge trap memory device for neuromorphic applications

# C. Van Dijck<sup>a,b,\*</sup>, F. Maudet<sup>a</sup>, C. Dubourdieu<sup>a,b</sup>, V. Deshpande<sup>a,\*</sup>

<sup>a</sup> Helmholtz-Zentrum Berlin, Institute Functional Oxides for Energy Efficient IT, Hahn-Meitner Platz 1, 14109 Berlin, Germany <sup>b</sup> Freie Universität Berlin, Physical Chemistry, Arnimallee 22, 14195 Berlin, Germany

## ARTICLE INFO

The review of this paper was arranged by Prof. Sorin Cristoloveanu

Keywords: Charge trap memory Amorphous GaOx 3-Terminal memory device

#### ABSTRACT

In this work, we demonstrate a 3-terminal field-effect based charge trap memory device with an amorphous- $GaO_x$  (a- $GaO_x$ ) layer fabricated at a low deposition temperature of 250°C. Utilizing the long life-time traps in the a- $GaO_x/Al_2O_3$  stack, we study the charge trap memory effect in the field effect devices. We observe more than one order of magnitude in channel current difference for two memory states with a retention of more than  $10^2$  s and endurance of 100 cycles. Our work paves a way for embedded a- $GaO_x$  memories for neuromorphic applications.

# 1. Introduction

Amorphous oxide semiconductors have been extensively studied for use in thin-film transistor display technology as they offer high conductivity combined with optical transparency. Their conductivity can be tuned through deposition processes and can be better than low temperature (<400°C) deposited amorphous or polycrystalline Si, making them suitable for back-end-of-line (BEOL) integration. Furthermore, metal oxide semiconductors also have several interesting properties, particularly the memristive property, which makes them suitable for memory applications. In this context, amorphous indium gallium zinc oxide (IGZO) and indium zinc oxide (IZO) have gained interest as materials for embedded DRAM and memories for synaptic application through BEOL integration on CMOS technology [1,2]. Amorphous gallium oxide  $(a-GaO_x)$  is a transparent conducting oxide with a wide bandgap (~4.9 eV) and can be n-type doped, yet it is much less investigated. The n-type doping in a-GaO<sub>x</sub> seems to result from oxygen defects [3,4]. Therefore, a-GaO<sub>x</sub> has the advantage of robust carrier density control as it does not require alloying or stable alloy composition, unlike other metal oxide semiconductors such as IGZO. Additionally, the low processing temperature of a-GaO<sub>x</sub> by atomic layer deposition enables applications such as BEOL integrated ultra-low power memories or embedded memories, which are intensely being pursued for neuromorphic and in-memory computing [5]. For neuromorphic computing, both volatility and non-volatility in memory devices is of interest, as volatile memories can be used for neuron functions and non-volatile ones for synaptic behaviour [6]. Therefore, devices that can be used as embedded DRAM (volatile) or as charge-trap transistors, memristors (non-volatile) are of great interest. Two terminal memristive devices are popular for BEOL integrated memories; they operate with write currents in the range  $10 - 100 \ \mu A \ (10 - 100 \ k\Omega$  resistance). Three terminal field effect devices have the advantage that they can operate at reduced currents in the nano ampere range (M $\Omega$  to G $\Omega$  resistance), leveraging the gate control of the current, and are thus useful for low power applications. Metal oxide channel field effect devices can be excellent candidates for ultra-low power BEOL memories for neuromorphic computing as they feature generally low current densities compared to filamentary memristors. In this work, we propose an a-GaO<sub>x</sub> channel non-volatile memory device, based on a charge trap mechanism resulting from charge traps near the a-GaO<sub>x</sub> channel and bottom oxide interface. We show that the memory effect survives several program and erase cycles, and the states have a retention of more than 100 s. We also show that multiple states can be obtained with repeated application of erase pulses demonstrating potentiation behaviour necessary for neuromorphic applications.

# 2. Device fabrication

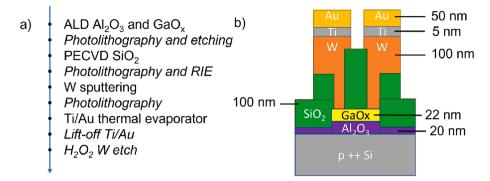

We fabricated a-GaO<sub>x</sub> conductive layer-based devices with 22 nm a-GaO<sub>x</sub> as the channel layer and 20 nm Al<sub>2</sub>O<sub>3</sub> as the bottom insulator on a highly doped  $p^{++}$  Si substrate. The a-GaO<sub>x</sub> thin film and Al<sub>2</sub>O<sub>3</sub> bottom oxide were deposited using plasma-enhanced atomic layer deposition

\* Corresponding authors at: Freie Universität Berlin, Physical Chemistry, Arnimallee 22, 14195 Berlin, Germany (C. Van Dijck). *E-mail addresses:* charlotte.vandijck@helmholtz-berlin.de (C. Van Dijck), veeresh.deshpande@helmholtz-berlin.de (V. Deshpande).

https://doi.org/10.1016/j.sse.2023.108717

Available online 26 July 2023 0038-1101/© 2023 The Authors. Published by Elsevier Ltd. This is an open access article under the CC BY license (http://creativecommons.org/licenses/by/4.0/).

Fig. 1. a) Process flow of the sample fabrication, b) cross-section schematic of the device stack.

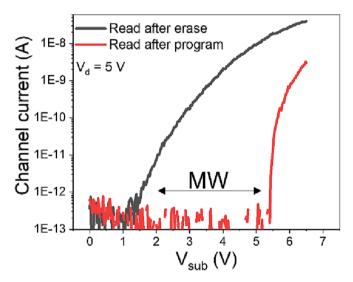

Fig. 2. Read current with field-effect of the a-GaOx layer after program (12 V for 500 ms) and erase (-7 V for 1 s) pulses for a device with 8 µm length and 10 µm channel width, indicating the memory window (MW). The substrate voltage is swept to 6.5 V with  $V_d = 5$  V.

(PEALD) at 250 °C. The a-GaOx PEALD process developed [3] allows tuning of the a-GaO<sub>x</sub> layer conductivity through O<sub>2</sub> plasma exposure time during each cycle of the deposition. The bottom oxide and channel were first deposited on a p<sup>++</sup> Si substrate. The channel mesa was then patterned using photolithography and etched by the resist developer. Afterwards, 100 nm SiO<sub>2</sub> was grown by plasma-enhanced chemical vapor deposition as the encapsulation layer and contacts in the layer were opened using CHF3-based reactive ion etching. A 100 nm thick W contact layer was then deposited by sputtering and patterned with a Ti (5 nm)/Au (50 nm) as hard mask during wet etching of the W in a 30% H<sub>2</sub>O<sub>2</sub> solution. The process flow is shown in Fig. 1a and the schematic of the resulting device in Fig. 1b. Devices with several channel lengths and widths were fabricated on the same chip. In this paper we discuss the results for devices with 10 µm channel width and 8 µm channel length. The electrical characterization of the devices was performed using a Keysight B1500 semiconductor parameter analyser.

#### 3. Results and discussion

The measurements of the current through the a-GaO<sub>x</sub> layer were performed by applying a voltage bias on the p<sup>++</sup> Si substrate (noted V<sub>sub</sub>) for field effect and a drain voltage (noted V<sub>d</sub>) across the channel layer. In order to demonstrate charge trap memory effect, the following measurements were performed. The device was subjected to a 'program' pulse (12 V on the substrate for 500 ms) and an 'erase' pulse (–7 V on

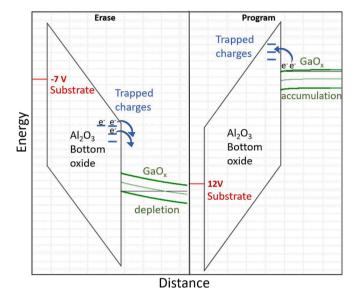

Fig. 3. Schematic band diagram showing the charge-trap mechanism during the erase and program states of the device [16].

the substrate for 1 s). After the program and the erase pulse a 'read' measurement was performed. The read measurement consisted of sweeping the substrate voltage from 0 to 6.5 V with a constant drain voltage of 5 V across the channel. The read current versus substrate voltage curves are shown in Fig. 2. A clear change in the channel current is observed between program and erase operations, confirming the memory effect. The mechanism we hypothesize is similar to the one of metal-nitride-oxide-silicon (MNOS) transistors [7]. The band diagram schematics for program and erase operations are shown in Fig. 3. Due to the high field, the gate oxide energy barrier has a trapezoidal shape. This condition is similar to Fowler-Nordheim (FN) tunneling case. However, here the charges only tunnel in and out of the trap states in the oxide to and from the conduction band of the channel layer. This tunnelling from trap states to the conduction band could be considered similar to FN tunnelling. During the erase state the negative voltage bias (-7 V) on the substrate brings the a-GaO<sub>x</sub> channel into depletion, allowing the interface traps in the Al<sub>2</sub>O<sub>3</sub> bottom oxide layer to de-trap electrons (and probably also inject holes from a-GaOx layer into deep traps in Al<sub>2</sub>O<sub>3</sub>) effectively increasing the net positive charge in the bottom oxide. It results in lowering the substrate voltage needed to accumulate carriers in the channel. Hence, one can obtain a high current at a read substrate voltage pulse of 6.5 V. Inversely, during the program operation, the positive voltage bias (12 V) on the substrate brings the a-GaO<sub>x</sub> layer into the accumulation region, allowing the electrons from the a-GaO<sub>x</sub> conduction band to be injected into the trap states in the Al<sub>2</sub>O<sub>3</sub> layer. It effectively increases the net negative charge in the bottom oxide (or

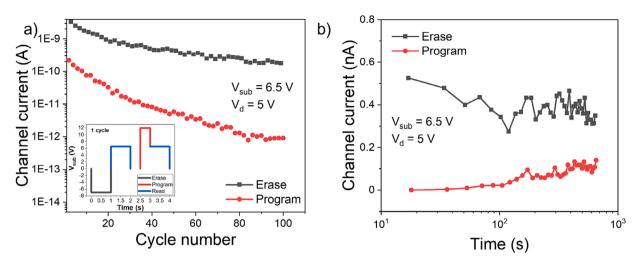

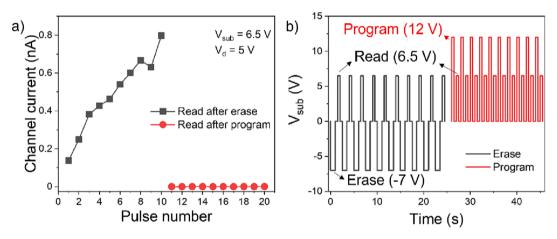

Fig. 4. a) Endurance and b) retention measurements for a device with 8  $\mu$ m length and 10  $\mu$ m channel width. The inset graph shows a schematic of the voltage pulses applied during 1 cycle. An erase pulse of -7 V for 1 s is applied, followed by a read pulse of 6.5 V and a program pulse of 12 V for 500 ms followed by the same reading pulse of 6.5 V. This is repeated for 100 cycles.

Fig. 5. a) Multiple states measurements showing 10 different states with erase pulses, followed by program pulses. Measurements data for a device with 8  $\mu$ m channel length and 10  $\mu$ m channel width. b) Schematic of the pulse voltage applied during the measurements shown in Fig. 5 a. An erase pulse of -7 V is applied for 1 s followed by a read pulse of 6.5 V. This cycle is repeated 10 times. Afterwards a program pulse of 12 V is applied for 500 ms and followed by a read pulse of 6.5 V and repeated 10 times.

lowers the net positive charge). As a result, a higher substrate voltage is needed to accumulate electrons in the channel. Hence, a lower current compared to the one in the erase state (due to low channel charge) is obtained at 6.5 V read substrate voltage pulse. While the conventional MNOS memory device has a tunnelling oxide and a charge trap oxide, here we have only one bottom oxide. Therefore, we believe that the charge traps are near the interface in the Al<sub>2</sub>O<sub>3</sub> bottom oxide. Prior studies indicate that there are deep traps in the Al<sub>2</sub>O<sub>3</sub>-Ga<sub>2</sub>O<sub>3</sub> interface, which might be present in our device [8]. While the absence of tunnel oxide could cause low retention, if the traps have long life-time the retention might still be sufficient for low power bio-realistic neuromorphic circuits [9,10] where time scales of several seconds to minutes are sufficient. We performed switching cycles (endurance measurement) for 100 cycles as shown in Fig. 4a. Although there is a drift in the current during the endurance measurements, the memory window is maintained and stabilizes after 80 cycles. Furthermore, the retention measurement on the device shows a clear memory window up to 650 s as shown in Fig. 4b. The memory window is decreased to around 200 pA after 650 s. While low current can be a limitation for classic high speed memory application, a difference of 200 pA can still be identified with sensitive amplifier circuits [11]. A recent work has shown neuron circuits operating with 100 pA range current [12]. The retention was measured after

the device had been cycled several times beforehand and therefore starts with a slightly lower current for both programmed and erased state compared to pristine state (1st cycle in endurance measurement; Fig. 4a). While the retention is lower compared to conventional charge-trap flash memory devices ( $>10^4$  s), it is still long enough to be utilized in low power neuromorphic circuits for bio signal processing [10]. Our devices exhibit conductance in the order of 20 nS, which is lower in comparison to similar works on amorphous oxide channel non-volatile devices, showing a range of 100–2000 nS [13–15]. The lower conductance value in our devices has the potential to enable lower power consumption in neuron circuits. Moreover, the ease of integration of these Al<sub>2</sub>O<sub>3</sub>-a-GaO<sub>x</sub> 3-terminal devices on BEOL of neuromorphic chips opens opportunities to develop hybrid neuromorphic circuits utilizing a-GaO<sub>x</sub> memory and Si CMOS transistors.

Finally, we investigated the possible presence of multiple memory states in these devices. To do so, we applied 10 consecutive erase pulses of -7 V and 1 s pulse width on the device. These pulses were followed by 10 program pulses of 12 V (500 ms pulse width). The results are presented in Fig. 5. We show that 10 different current states can be reached with repeated application of erase pulses. Thus, the device has potential for use in electronic neuron circuits as it can demonstrate integration of erase pulses and has slow decay of the current state (inferred from lower

retention in Fig. 4b). The program pulse application shows binary nature and leads to abrupt drop in current. These are promising first results on BEOL compatible oxide channel material and can be further optimized through stack engineering and electrical programming optimization.

# 4. Conclusion

We demonstrated a low temperature (250 °C) ALD-grown conductive a-GaO<sub>x</sub> based memory device. Based on the charge traps in the oxide channel - gate oxide stack, programmed and erased current states with a ratio of more than one order of magnitude were obtained. The states also show a retention of more than  $10^2$  s and are stable over several cycles. By application of several identical erase pulses about 10 distinguishable states are obtained, demonstrating the potential for neuromorphic applications. As this is a novel demonstration of a 3-terminal a-GaO<sub>x</sub> based memory device, further engineering of the stack can be done to improve the stability of memory states. Furthermore, adding an extra blocking or tunnelling oxide as in the MNOS devices could improve the retention towards embedded memory applications. Our work demonstrates a novel amorphous oxide material-based device for BEOL-integrated memories for neuromorphic applications.

# **Declaration of Competing Interest**

The authors declare that they have no known competing financial interests or personal relationships that could have appeared to influence the work reported in this paper.

# Data availability

Data will be made available on request.

# Acknowledgement

The experimental work was performed in the framework of GraFOx II, a Leibniz-ScienceCampus partially funded by the Leibniz Association.

#### References

- Yin H, Hyun J, Park Y, Kim S, Lim H, Min Y, et al. Program/erase characteristics of amorphous gallium indium zinc oxide nonvolatile memory. IEEE Trans Electron Dev 2008;55(8):2071–7.

- [2] Belmonte A, et al. Tailoring IGZO-TFT architecture for capacitorless cycles endurance and L<sub>g</sub> scalability down to 14nm. IEEE Int Electron Dev Meet 2021: 226–9.

- [3] Kröncke H, et al. Effect of O<sub>2</sub> plasma exposure time during atomic layer deposition of amorphous gallium oxide. J Vac Sci Technol A 2021;39(5). 052408.

- [4] Kim J, Sekiya T, Miyokawa N, Watanabe N, Kimoto K, Ide K, et al. Conversion of an ultra-wide bandgap amorphous oxide insulator to a semiconductor. NPG Asia Mater 2017;9(3):e359-.

- [5] Sebastian A, Le Gallo M, Khaddam-Aljameh R, Eleftheriou E. Memory devices and applications for in-memory computing. Nat Nanotechnol 2020;15(7):529–44.

- [6] Kuzum D, et al. Synaptic electronics: materials, devices and applications. 382001 Nanotechnology 2013;24. https://doi.org/10.1088/0957-4484/24/38/382001.

[7] Sze SM, Ng KK, editors. Physics of Semiconductor Devices. Wiley; 2006.

- [7] Size Sin, Ng Ng Cutobs. Highest of Schneondarten Devices. Whey, 2000.

[8] Roy S, et al. In Situ Diselectric Al<sub>2</sub>O<sub>3</sub> β-Ga<sub>2</sub>O<sub>3</sub> Interfaces Grown Using Metal-Organic Chemical Vapor Deposition. Adv Electron Mater 2021;7(11):2100333. https://doi. org/10.1002/aelm.202100333.

- [9] Covi E, Donati E, Liang X, Kappel D, Heidari H, Payvand M, et al. Adaptive Extreme Edge Computing for Wearable Devices. 611300 Front Neurosci 2021;15. https:// doi.org/10.3389/fnins.2021.611300.

- [10] Chicca E, Indiveri G. A recipe for creating ideal hybrid memristive-CMOS neuromorphic processing systems. Appl Phys Lett 2020;116:120501. https://doi. org/10.1063/1.5142089.

- [11] B. Goldstein et al., CMOS low current measurement system for biomedical applications, in: IEEE 2011 IEEE International Symposium on Circuits and Systems (ISCAS), 1017-1020, 2011, doi:10.1109/ISCAS.2011.5937741.

- [12] Singh AK, Saraswat V, Baghini MS, Ganguly U. Quantum Tunneling Based Ultra-Compact and Energy Efficient Spiking Neuron Enables Hardware SNN. IEEE Trans Circuits Syst 2022;69(8):3212–24.

- [13] Park J, Jang Y, Lee J, An S, Mok J, Lee S-Y. Synaptic Transistor Based on In-Ga-Zn-O Channel and Trap Layers with Highly Linear Conductance Modulation for Neuromorphic Computing. 221306 Adv Electr Mater 2023;9(6). https://doi.org/ 10.1002/aelm.202201306.

- [14] Li Ya, Pei Yanli, Ruiqin Hu, Chen Zimin, Ni Yiqiang, Lin Jiayong, et al. Charge Trapping Memory Characteristics of Amorphous-Indium-Gallium-Zinc Oxide Thin-Film Transistors With Defect-Engineered Alumina Dielectric. IEEE Trans Electr Dev 2015;62(4):1184–8.

- [15] Kim JS, Kang S, Jang Y, Lee Y, Kim K, Kim W, et al. Investigating the reasons for the difficult erase operation of a charge-trap flash memory device with amorphous oxide semiconductor thin-film channel layers. Phys Status Solidi RRL 2021;15(2): 2000549.

- [16] Southwick RG, Sup A, Jain A, Knowlton WB. An Interactive Simulation Tool for Complex Multilayer Dielectric Devices. IEEE Trans Dev Mater Reliab 2011;11(2): 236–43.